请教时序约束的问题

设置好 false path

能具体一些吗,设置false path后好象实际工作反而不正常。

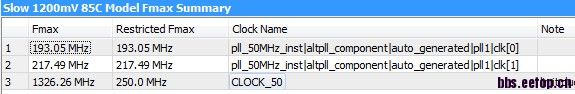

另外Quartus II报告中的fmax是在排除了时序违例之后的最高频率吗?谢谢

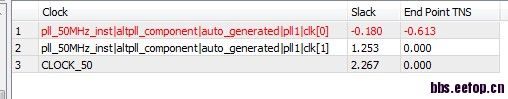

CLK[1]约束只要求50M, CLK[0]约束200M,但setup还是有违例,能够调整优先级吗。

小编说的好像不太清楚,这里有两个解决办法:

1。从设计的角度把50M和200M的两个时钟按照异步处理,注意跨时钟域的问题--加异步时钟约束

2。直接生成200MHz时钟,然后四分频得到50MHz, 在设计的时候作为同步处理--不用额外加约束,不过设计的时候要注意从200M到50M的信号需要展宽,这里有一个相位对齐的问题。

这两个clock domain之间做异步处理了,设置false path就行了,不过fpga中正常的综合和实现,只有局部逻辑能run到200MHz哦,一般timing好像达不到那么快的。

我试试,多谢各位,我是只需要局部200M,IO只需要15K左右就可以了

如果是局部200MHz, 可以用资源换频率,在FPGA资源允许的情况下内部做多路,那么频率就成倍的将下来了.

高温最慢库180ps的Slack可以忽略,完全不影响实际工作。

小编说的好像不太清楚,这里有两个解决办法:

1。从设计的角度把50M和200M的两个时钟按照异步处理,注意跨时钟域的问题--加异步时钟约束

--如果是同一个锁相环,可以做同步处理

2。直接生成200MHz时钟,然后四分频得到50MHz, 在设计的时候作为同步处理--不用额外加约束,不过设计的时候要注意从200M到50M的信号需要展宽,这里有一个相位对齐的问题。

--尽量用FPGA带的锁相环,好处很多,如果使用分频得到的时钟,至少必须做异步处理,因为普通触发器的Jitter很大,而且在上全局时钟资源的话,时钟延迟每次布局布线都会变化

超的都是85度的低电压慢速库,时钟是用PLL之后的输出了。