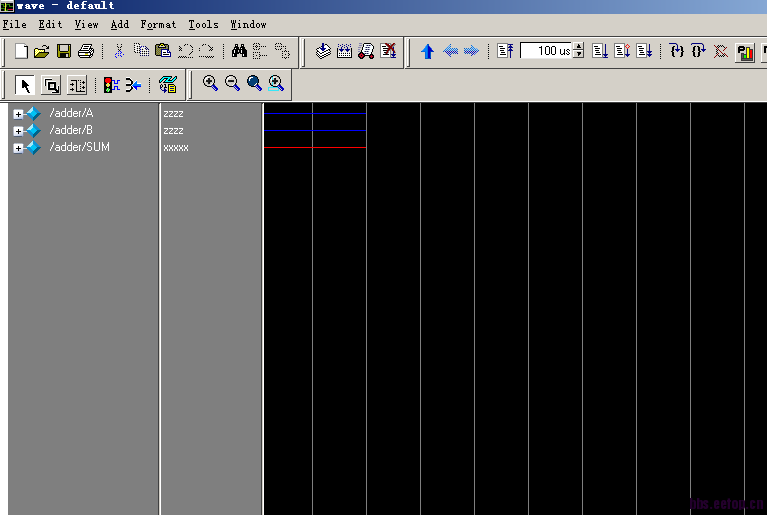

Modesim 仿真时为什么波形总是高阻值?蓝色线

// 程序名称 : adder.v

// 日 期 : 2001/2/20

//*********************************************************

// 定义模块(module)

//*********************************************************

module adder( A, B, SUM );

input [3:0] A; // 四位加法器的加数输入线

input [3:0] B; // 四位加法器的被加数输入线

output [4:0] SUM; // 包括进位的四位加法器输出

// 利用Verilog HDL加法运算子设计出的加法器

assign SUM = A + B;

//*********************************************************

endmodule

测试激励如下

/ 实验名称 : 加法器

// 程序名称 : tb_adder.v(测试平台)

// 日 期 : 2002/1/21

module tb_adder();

reg [3:0] tb_A; // 用来仿真加数的输入

reg [3:0] tb_B; // 用来仿真被加数的输入

wire [4:0] tb_SUM; // 用来连接加法器包括进位的输出

//*********************************************************

// 激活仿真后的时序设定

//*********************************************************

initial

begin

// 仿真开始时将加数的输入设定为0000,被加数的输入设定为0000。

tb_A <= 4'b0000;

tb_B <= 4'b0000;

// 经过100个时间单位后,将加数的输入改为0101

#100 tb_A <= 4'b0101;

// 再经过100个时间单位后,将加数的输入改为1010

#100 tb_A <= 4'b1010;

// 再经过100个时间单位后,将加数的输入改为1111

#100 tb_A <= 4'b1111;

// 再经过100个时间单位后,将加数的输入改回0000

// 同时将被加数的输入改为0101

#100 tb_A <= 4'b0000;

tb_B <= 4'b0101;

// 再经过100个时间单位后,将被加数的输入改为1010

#100 tb_B <= 4'b1010;

// 再经过100个时间单位后,将被加数的输入改为1111

#100 tb_B <= 4'b1111;

// 再经过100个时间单位后,将加数的输入改为1111

#100 tb_A <= 4'b1111;

// 再经过100个时间单位后,将加数的输入改回0000

// 同时将被加数的输入也改回0000

#100 tb_A <= 4'b0000;

tb_B <= 4'b0000;

// 再经过100个时间单位后结束仿真。

#100 $finish;

end

//*********************************************************

// 加载并且连接准备仿真的加法器模块

//*********************************************************

adder adder(

// 将tb_A讯号连接到adder的A port

.A( tb_A ),

// 将tb_B讯号连接到adder的B port

.B( tb_B ),

// 将tb_SUM向量讯号连接到adder的SUM port

.SUM( tb_SUM )

);

//*********************************************************

endmo

dule

dule

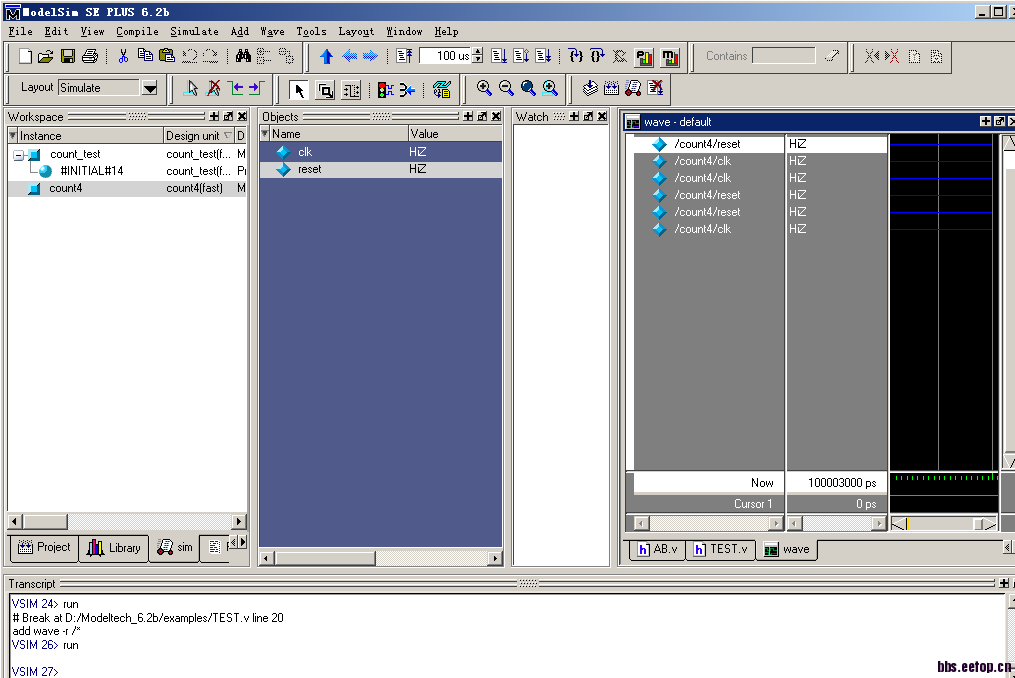

另外一个计数器的测试也是出现高阻值,程序如下:

module count4(out,reset,clk);

output[3:0] out;

input reset,clk;

reg[3:0] out;

initial ;

always @(posedge clk)

begin

if (reset) out<=0; //?

else out<=out+1; //?

end

endmodule

激励:

module count_test;

reg clk,reset;

wire [3:0] out;

count4 i1(

.out(out),

.reset(reset),

.clk(clk)

);

initial

clk=0;

always

#10 clk=~clk;

initial

begin

#1000 reset=0;

#1000 reset=1;

#500 reset=0;

#500 reset=1;

$stop;

end

endmodule

刚接触这个

不是很会

求高手指点

好像见过类似问题,有可能是visual界面的选项勾错了。直接在transcript里敲命令试试,只用最基本的选项。

vlog,vsim,add wave,run

跟“visual界面的选项勾错”那个相关啊?

记得是simulation这一步的对话框里。我也不能确定是不是这个问题,你先用命令试试。

呵呵

自己找到原因了

LZ 什么原因啊 我跟你一样的问题啊 困扰我好久了

这种问题先看时钟 复位 输入激励

没问题再看有没有multi-drive

再查其他问题 仿真阶段的问题好处理

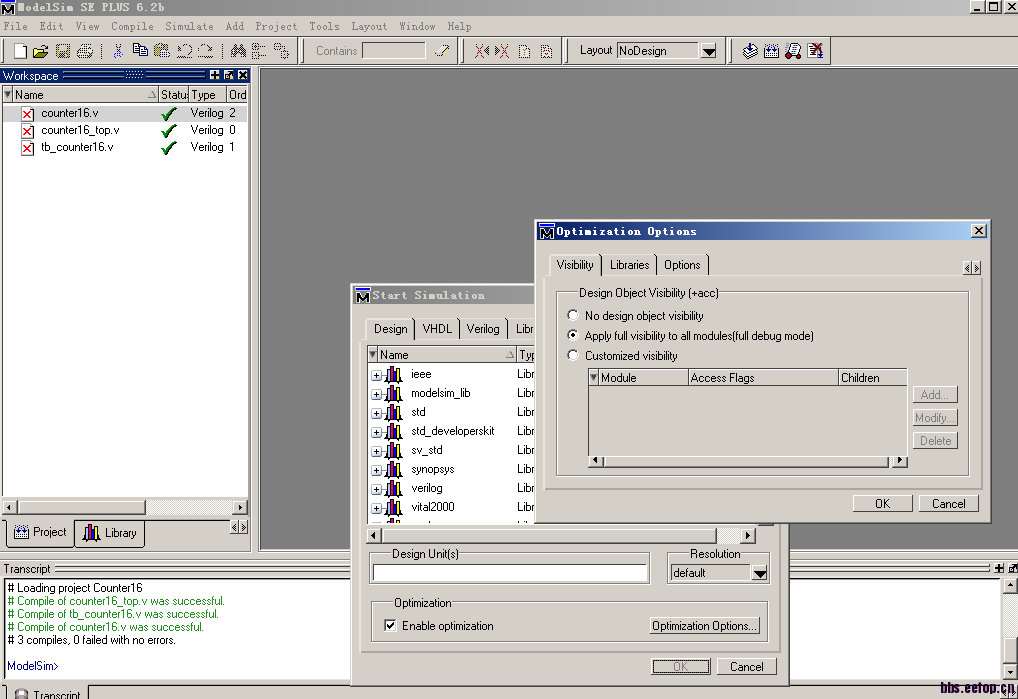

这个你试试simulate下面

在start simulate >>>optimization option>>apply full visiblity to all module试试看

截图如下

使用VCS就没有这些问题,直接run就好了,我就是用的vcs,有时候就不用查看GUI界面,直接看打印结果就可以验证功能仿真的正确性,比看波形直观的多,建议大家使用一下vcs

小编你第一个例子里面的Testbench里面赋值可能有点问啊。当然这个和输入高阻态没什么关系。只是达不到你注释里面的那个功能。