请教跨时钟域数据传输的问题

时间:10-02

整理:3721RD

点击:

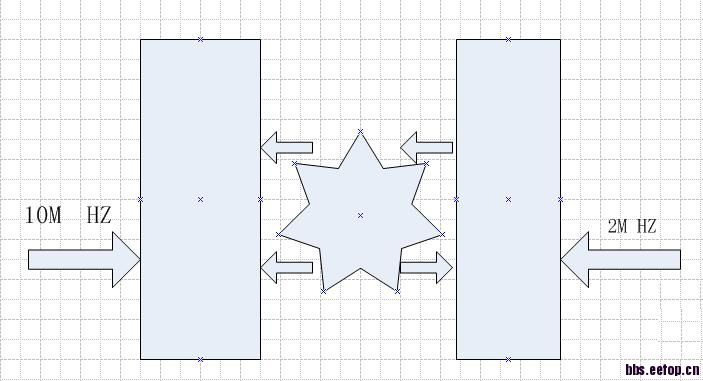

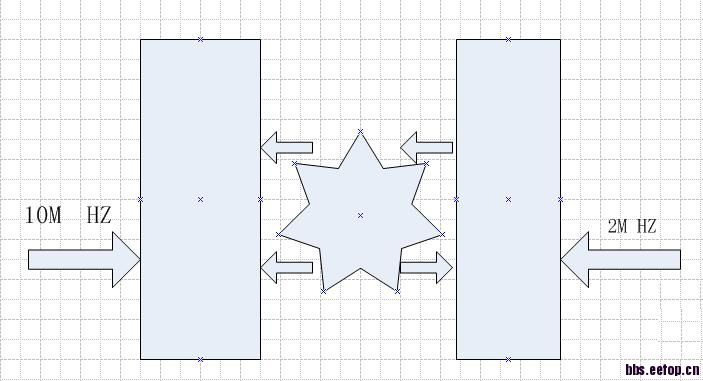

如果两个时钟频率差别很大,如何进行数据传输

网上看到的基本都是双FF的同步结构,貌似不太合适

请问如何实现数据传输?

网上看到的基本都是双FF的同步结构,貌似不太合适

请问如何实现数据传输?

简单的握手就可以了,异步FIFO最常见的

嗯,对,看了这个帖子还不错。我再看看

http://bbs.ednchina.com/BLOG_ARTICLE_253787.HTM

双FF的方法只适用于单个信号的情况,多根总线的情况虽然可以避免亚稳态,但数据不一定是对的

简单的握手就可以了,异步FIFO

FIFO就可以...

不过,如果数据是完全连续的..中间任何时候都是有效数据的传输..那么这种问题就没有办法解决

握手信号就可以了 ,两个dff是为了同步用的

这个要分情况:

如果单纯只是控制信号的跨时钟域,两级ff同步就可。

如果是databus的跨时钟域(也就是说多于1个bit的数据),就需要异步fifo。

从慢到快,双FF即可。从快到慢,要用一些技巧,我忘记那个原理图是咋画的了

fifo吧~

最稳健高效的方法应该是两个异步FIFO,只是会消耗比较多的资源。

握手也可以,不过要消除亚稳态需要经过两级寄存器才行,经过一级是不太可靠的。

并且如果两边时钟差别比较大的话,握手效率会比较低。

1.单个信号采用双DFF方式, 此方式只能帮你解决亚稳态, 不保证信号的正确性。

2.如果说是总线类得信号, 推荐采用格雷码的方式。

3. 数据类推荐采用异步FIFIO方式。

单比特信号同步,从快到慢,可能需要沿展宽

多比特:如果是连续变化的,可转化成gray-code形式,用DFF同步

如果不是连续的,则用握手(DMUX),或者异步FIFO。

学习下啦