采用四级流水线的加法器综合有问题(请教)

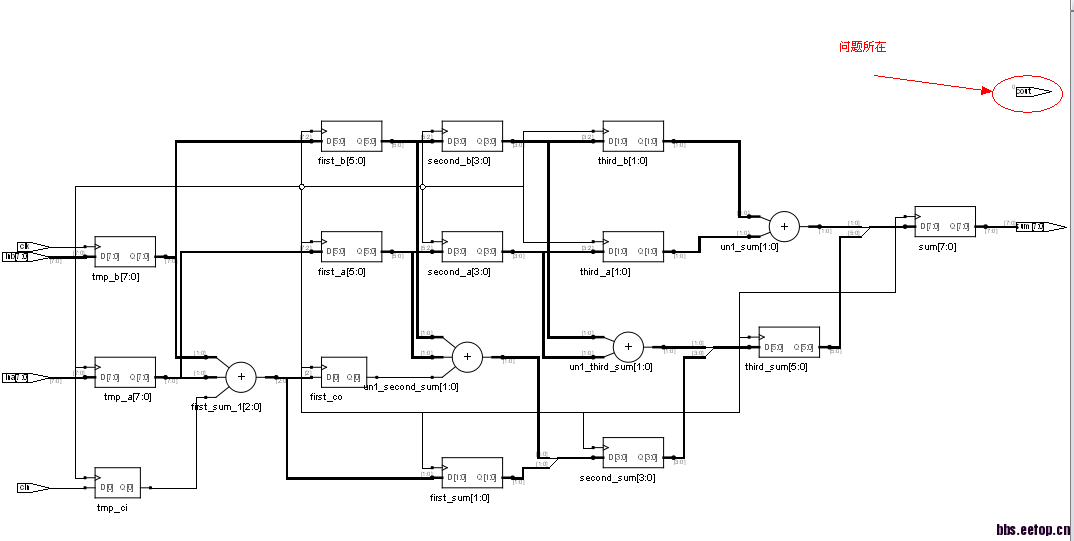

如题,写了一段采用四级流水线的加法器,在对比几种设计方法的性能。但用Symply pro综合后RTL图有问题。不知为什么综合后cout和前面的链接断开了。特此请教。谢谢。

源码如下:

//////////////////////////////////////////////////////////////////////////////////

// Company: -------

// Engineer: -------

//

// Create Date: 17:29:02 03/12/2012

// Design Name: 流水线技术在加法器上的应用

// Module Name: adder_pipe4

// Project Name: 四级流水加法器

// Target Devices: XC3S500E-4PQ208

// Tool versions: ISE12.4

// Description:

//////////////////////////////////////////////////////////////////////////////////

module adder_pipe4(cout, sum, ina, inb, cin, clk);

//定义输入、输出变量

input [7:0] ina, inb;

input cin, clk;

output reg [7:0] sum;

output reg cout;

//定义中间变量

reg [7:0] tmp_a, tmp_b;

reg tmp_ci, first_co, second_co, third_co;

reg [1:0] first_sum, third_a, third_b;

reg [3:0] second_a, second_b, second_sum;

reg [5:0] first_a, first_b,third_sum;

//输入数据缓存

always @ (posedge clk)

begin

tmp_a = ina;

tmp_b = inb;

tmp_ci = cin;

end

//第一级流水

always @ (posedge clk)

begin

//第一级加(低两位)

{first_co, first_sum} = tmp_a[1:0] + tmp_b[1:0] + tmp_ci;

//未参加计算的数据缓存

first_a = tmp_a[7:2];

first_b = tmp_b[7:2];

end

//第二级流水

always @ (posedge clk)

begin

//第二级加(第2,3位)

{second_co, second_sum} = {first_a[1:0] + first_b[1:0] + first_co, first_sum};

//数据缓存

second_a = first_a[5:2];

second_b = first_b[5:2];

end

//第三级流水

always @ (posedge clk)

begin

//第三级加(第4,5位)

{third_co, third_sum} = {second_a[1:0] + second_b[1:0] + second_co,second_sum};

//数据缓存

third_a = second_a[3:2];

third_b = second_b[3:2];

end

//第四级流水

always @ (posedge clk)

begin

//第四级加(第7,8位)

{cout, sum} = {third_a[1:0] + third_b[1:0] + third_co, third_sum};

end

endmodule

有什么问题,RTL 知识帮助你了解设计的大致结构,跟综合后的结果可能差距很大,没有多大参考价值。

还有,如果你使用的altera的FPGA,做个加法器完全没必要这么做,就按照普通那样的写法,性能也会很高,位宽在20bit以内的,跑150m以上没有任何问题,因为ALM内有加法器和高速互联资源

在ASIC设计中,才会涉及到高速加法器的设计

您好,我用的是Xilinx的器件,在对比几种设计方法的性能。不知为什么综合后cout和前面的链接断开了。

改改这种写法吧{second_co, second_sum} = {first_a[1:0] + first_b[1:0] + first_co, first_sum};

先用3bit wire 代替 wire [2:0] wire_tmp3 = first_a[1:0] + first_b[1:0] + first_co;

然后{second_co, second_sum} = {wire_tmp3, first_sum};

改改这种写法吧{second_co, second_sum} = {first_a[1:0] + first_b[1:0] + first_co, first_sum};

先用3bit wire 代替 wire [2:0] wire_tmp3 = first_a[1:0] + first_b[1:0] + first_co;

然后{second_co, second_sum} = {wire_tmp3, first_sum};

改一下试试。

谢谢,成功实现。

你的第二级进位second_co就没有生成

您好,可否讲解一下原理。俗话说售之以鱼,不如售之以渔。

按五楼的写法,可以实现了。正在考虑细节。

你把综合工具想的太智能了,运算前后的位宽不匹配,最高位丢失

你看看netlist就知道了