向各位牛人请教:ALTERA FPAG 复位信号是高电平好还是低电平好?

请问各位牛人:ALTERA FPAG 复位信号是高电平好还是低电平好?

谢谢!

牛人们出来冒个泡吧!

無所謂吧,這個應該和FPGA沒關係,應該和你的邏輯相關的

好像都是低电平复位吧。

低电平复位时,我们一般要这样写:always@(posedge clk or negedge reset_n)

if(!reset_n)

begin

.............

end

else

begin

.....................

end

高电平复位时,我们一般这样写:always@(posedge or posedge reset)

if(reset)

begin

.............

end

else

begin

.....................

end

这样综合出来的结果没有区别吗?

期待高人回答!期待大虾出现解答,谢谢!

期待大侠!

看看你的IP核,Xilinx的IP核都是高复位,自己的逻辑一般也就高复位(比如fifo等),保持一致,设计比较清晰。不常用Alter,如果ALTER的IP核默认的复位是低电平,你逻辑里的复位最好也是低。这样就不用再取反得到复位

一般版级上的都是低复位

谢谢!

应该没有差别吧,个人喜好

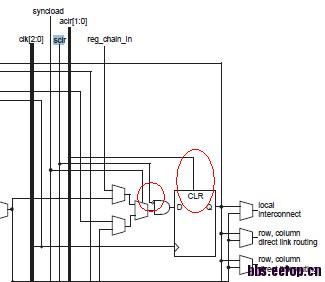

内部D触发器自带的复位时低有效的,如果你用高有效复位的话,徒增组合逻辑,浪费资源,还是用低电平复位好

学习了,谢谢!

看器件自身吧,如果器件本身是低电平的,那就低电平复位,altera用低电平复位的多点。

XILINX的FAE强烈推荐采用高电平同步复位,所以我们现在都用高电平复位。

TI EETOP社区免费在线视频,还可获取积分兑换!

一般都是低电平复位吧,低电平也就是指接地信号,接地信号容易受到干扰,产生毛刺..所以一般用低电平复位,高电平作为正常工作电平...

看你FPGA外面的硬件是怎么接的撒,

硬件一般低电平复位,低电平也有利于DFT设计

看看reuse methodology manual

你们都没有看Altera的FPGA结构吗?它们的复位信号都是高电平和低电平可选的,不过在同一个LAB中,只能用同一种电平。

这个具体得看芯片手册,以StratixIV系列为例

altera的低电平异步复位,xilixn的高电平同步复位。和两个公司的底层结构有关

我觉得这个好像没有什么大的差别,只是需要注意一下就行了