请教一个小的问题

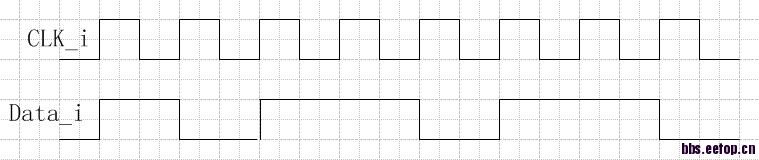

波形

module test(reset,clk_i,data_i,counter);

input reset;

input clk_i;

input data_i;

output [7:0] counter;

reg [7:0] counter;

reg data_i_reg;

always @ (negedge clk_i or negedge reset)

begin

if (!reset)

begin

counter <= 0;

end

else

begin

data_i_reg <= data_i;

if (!data_i && data_i_reg)

begin

counter <= counter + 1;

end

end

end

endmodule

随便写的一个,试试看吧

begin data_i_reg <= data_i;

if (data_i && !data_i_reg)

begin

counter <= counter + 1;

end

end

你好,非常感谢,你的方法是正确的,就是变成在data_i的下降沿计数了,

这只是一个小问题

我对verilog还是缺乏理解

begin 和end之间的两段赋值顺序是如何定义的?

假如在时钟上升沿,data_i也是上升沿跳转为1

这时候data_i_reg <= data_i;中的data_i_reg跳转为1

而if语句里面的两个变量分别是1还是0呢?

在时钟的上升沿,执行下面语句

begin

phrase1 data_i_reg <= data_i;

1 1

if (data_i && !data_i_reg)

1 0

begin

phrase2 counter <= counter + 1;

end

end

phrase1和phrase2 同时执行,if语句里的data_i_reg保留上个时钟的值,data_i为该上升沿定义的值

对不?