testbench 中for 循环中用= 还是<= ?

下面这段代码中,红色的如果替换成<=, 即非阻塞, 仿真结果有很大差别,这是怎么回事?

initial

begin

for (i=6;i>=0;i=i-1)

begin @(posedge clk); w_i=simarray ;

endend

一般都这样写:

always @(posedge clk) begin

for (i=6;i>=0;i=i-1)

w_i <= simarray;

end

如果只是initial

initial begin

@(posedge clk);

for (i=6;i>=0;i=i-1)

w_i = simarray;

end

这怎么可能? @(posedge clk) 被放于 for 循环之外,岂不是来一次clk,则整个for 都循环完了? 我试过了,不行。

你这个是initial嘛

一个是一个cycle做一次,另一个是一个cycle 6次全部都完成。在initial里面我感觉区别不大。

你需要详细说一下需要产生什么样的激励

仿真结果有什么差别呀?有图有真相

模块代码如下:

module simple_fsm (clk, rst_n,w_i,z_o);

input clk;

input rst_n;

input w_i;

output z_o;

reg z_o;

reg [1:0]current_state;

reg [1:0] next_state;

parameter idle=2'b01;

parameter s0 =2'b10;

parameter s1 =2'b11;

always@(posedge clk)

begin

if (rst_n==1'b0)

current_state<=idle;

else

current_state<= next_state;

end

always@(*)

begin

next_state=current_state;

case (current_state)

idle: if (w_i==1'b1) next_state=s0;

else next_state=idle;

s0 : if (w_i==1'b1) next_state=s1;

else next_state=idle;

s1 : if (w_i==1'b1) next_state=s1;

else next_state=idle;

default : next_state=idle;

endcase

end

always@(posedge clk)

begin

if (!rst_n) z_o=1'b0;

else

case (current_state)

idle: z_o=1'b0;

s0 : z_o=1'b0;

s1 : z_o=1'b1;

default : z_o=1'b0;

endcase

end

endmodule

Testbench 如下:

module simple_fsm_tb ();

reg clk;

reg rst_n;

reg w_i;

integer i;

wire z_o;

event start;

reg simarray [6:0] ;

always

#10 clk=~clk;

initial

begin

clk=1'b0;

rst_n=1'b1;

#6 rst_n=~rst_n;

#6 rst_n=~rst_n;

-> start;

end

initial $readmemb("simarray.txt", simarray);

initial begin

@(start);

for (i=6;i>=0;i=i-1) begin @(posedge clk); w_i=simarray ;end //simarray;

//@(posedge clk); w_i<=1'b1;

//@(posedge clk); w_i<=1'b0;

//@(posedge clk); w_i<=1'b1;

//repeat(2) @(posedge clk) w_i=1'b0;

//repeat(2) @(posedge clk) w_i=1'b1;

//@(posedge clk); w_i<=1'b0;

end

initial $display ("Test control");

always begin

@(posedge clk); if (z_o==1'b1) $display("got one");

end

simple_fsm simple_fsm_0 (

.clk (clk),

.rst_n(rst_n),

.w_i(w_i),

.z_o(z_o)

);

endmodule

模块代码如下:

module simple_fsm (clk, rst_n,w_i,z_o);

input clk;

input rst_n;

input w_i;

output z_o;

reg z_o;

reg [1:0]current_state;

reg [1:0] next_state;

parameter idle=2'b01;

parameter s0 =2'b10;

parameter s1 =2'b11;

always@(posedge clk)

begin

if (rst_n==1'b0)

current_state<=idle;

else

current_state<= next_state;

end

always@(*)

begin

next_state=current_state;

case (current_state)

idle: if (w_i==1'b1) next_state=s0;

else next_state=idle;

s0 : if (w_i==1'b1) next_state=s1;

else next_state=idle;

s1 : if (w_i==1'b1) next_state=s1;

else next_state=idle;

default : next_state=idle;

endcase

end

always@(posedge clk)

begin

if (!rst_n) z_o=1'b0;

else

case (current_state)

idle: z_o=1'b0;

s0 : z_o=1'b0;

s1 : z_o=1'b1;

default : z_o=1'b0;

endcase

end

endmodule

Testbench 如下,请把红色的改成非阻塞,仿真结果不一样,这是怎么回事:

module simple_fsm_tb ();

reg clk;

reg rst_n;

reg w_i;

integer i;

wire z_o;

event start;

reg simarray [6:0] ;

always

#10 clk=~clk;

initial

begin

clk=1'b0;

rst_n=1'b1;

#6 rst_n=~rst_n;

#6 rst_n=~rst_n;

-> start;

end

initial $readmemb("simarray.txt", simarray);

initial begin

@(start);

for (i=6;i>=0;i=i-1) begin @(posedge clk); w_i=simarray [ i ];end ;

//@(posedge clk); w_i<=1'b1;

//@(posedge clk); w_i<=1'b0;

//@(posedge clk); w_i<=1'b1;

//repeat(2) @(posedge clk) w_i=1'b0;

//repeat(2) @(posedge clk) w_i=1'b1;

//@(posedge clk); w_i<=1'b0;

end

initial $display ("Test control");

always begin

@(posedge clk); if (z_o==1'b1) $display("got one");

end

simple_fsm simple_fsm_0 (

.clk (clk),

.rst_n(rst_n),

.w_i(w_i),

.z_o(z_o)

);

endmodule

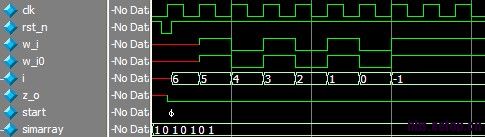

防了一下,没差别呀,w_i和w_i0是我分别用阻塞和非阻塞赋值的结果