急请求高手指点:verilog中if条件识别不了是什么原因?

用测试文件仿真时,发现源程序代码中if后面的条件明明是满足的,可是仿真的结果显示的是程序并没有识别这个条件,感觉很奇怪啊!

接触verilog不久,老是遇到些奇怪的现象,估计是一些规则还没有掌握,还请路过的高手指点,不胜感激!

出错部分代码为:

if(b1==b2==0&a2==1&a1==0) begin

dependa<=1;

AO<=~AO;

state<=edgecount;

end

else

if(a1==a2==1&b2==0&b1==1) begin

dependb<=1;

BO<=~BO;

state<=edgecount;

end

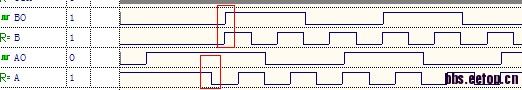

仿真波形如下:

程序的本意是:A和B信号边沿先到的那个对应的输出先翻转(AO为A对应的输出,BO为B对应的输出)。激励信号是A的边沿先到,理应AO先翻转,但是程序运行下来却是BO先翻转。

被这个问题困惑着,希望有高手能指点迷津。

&和&&搞错了吧

我程序中有其他的条件也是用&,是可以识别的呢......

要用& 就把 其它的条件表达式用()括起来

您说的是这样的么:if((b1==b2==0)&(a2==1)&(a1==0))?

试了一下,好像不是因为这个呢......

为什么要写成 b1==b2 == 0

写code 不要追求简洁, 而是尽量避免歧义

对不起,您两次发表间隔少于 45 秒,请不要灌水!

b1 =1;b2 =0;

$display(" %b",b1==b2==0); ---得到1

b1 =1;b2 =1;

$display(" %b",b1==b2==0); ---得到0

b1 =0;b2 =0;

$display(" %b",b1==b2==0); ---得到0

你要表达的是逻辑与(&&)关系吧 这里你用了位&

顶7楼,而且注意一下&&是逻辑与,&是位与

a1,a2,b1,b2与输入信号A与B的关系是什么样的?

在仿真时,可以把这四个内部信号添加到波形界面,然后再比对一下程序中的判断条件,就会知道问题在哪的

把 b1==b2==0这样形式的语句分开来写,对于单bit来说&& 与 & 没有区别,不过要是多bit就有区别了。

小编的意思是判断,b2与b1都等于0的情况,但是如果连起来写,若b1 == b2,此时( (b2==b1) == 1)!=0。小编可以测试一下。

我怀疑是A1 A2 B1 B2 的程序有点问题

我觉得是时钟的问题。你程序的结构是 几个and gate + mux + reg.所以应该是在A/B的沿来临,并且posedge clk来的时候寄存器置位,而是在下一个clk输出。所以请问是不是clk的问题,能否发一个带clk的仿真图?

不见小编了

这么多人给你出主意 寒心啊

那玩意儿不能写成连等吧

学习了!

假设你的边沿检测的那部分代码没有问题............

那么你知道

“b1==b2==0&a2==1&a1==0”这一段什么时候能执行么?

答案是:

b1=1

b2=0

a2=1

a1=0

你确定这个是你要判断的逻辑满足条件?

因为不知道你这个b1,b2,a1,a2是什么信号,不好说你判断对否......

问题肯定就在这里了...你对连续判断的理解有误...这是个从右向左的比较顺序

a1==a2==1这个表达式自右向左结合,首先计算a2==1 得带一个逻辑值x,再计算a1==x。

你的代码描述的就是仿真的逻辑,你自己语言学的不好。if(b1==b2==0&a2==1&a1==0)

意思是 b1 == 1 b2 == 0 a2 ==1 a1 == 0