双口RAM求助

时间:10-02

整理:3721RD

点击:

小弟新学FPGA想做一个双口RAM,当A部分写完的时候开始写B部分(先光写不读),代码如下:

本人有几个疑惑的地方:求高手能给小弟解答一下

1. 初始状态下的写使能该如何确定下来呢?按我这样的写法可以么?

2. 这里我用地址自动计数到31时,在时钟周期到来时控制写使能,在下一时钟周期到来时控制写入数据流的方向。按我这样的写法可以么?

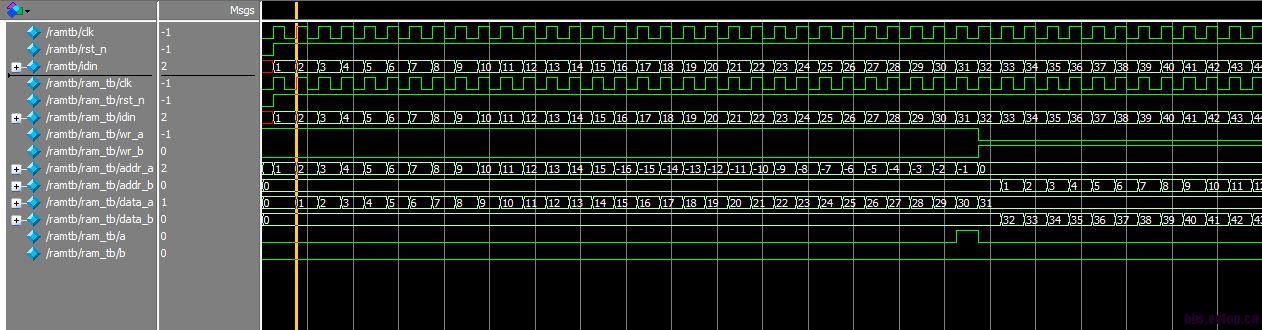

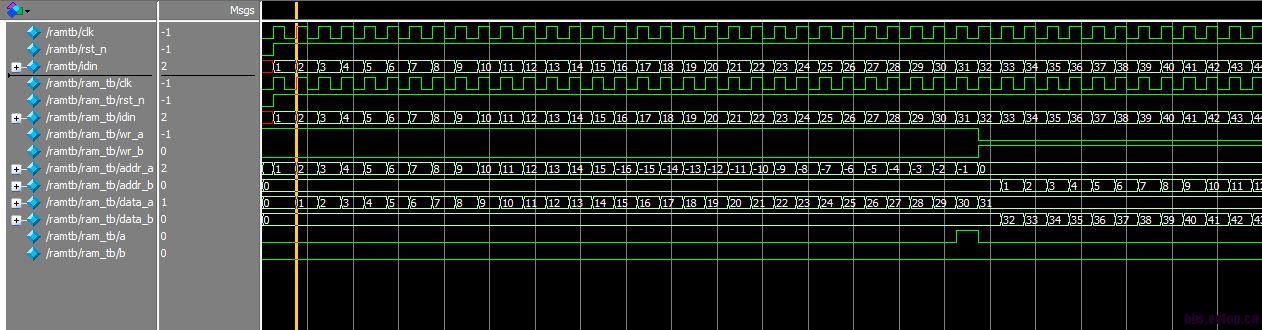

3. 仿真发现只到第31个地址的时候就翻转了,理论上应该到32才翻转的,而且地址怎么过了15之后就出现负值了, 这个很奇怪。

module ram ( clk, rst_n, idin);

input clk;

input rst_n;

input [7:0] idin;

reg wr_a , wr_b;

reg [4:0] addr_a, addr_b;

reg [7:0] data_a, data_b;

wire a ,b;

assign a = addr_a == 'b1_1111 ? 1 : 0;

assign b = addr_b == 'b1_1111 ? 1 : 0;

always @ (posedge clk or negedge rst_n)

if (!rst_n)

begin

wr_a <= 1'b1;

wr_b <= 1'b0;

end

else if (a)

begin

wr_a <= 1'b0;

wr_b <= 1'b1;

end

else if (b)

begin

wr_a <= 1'b1;

wr_b <= 1'b0;

end

always @ (posedge clk or negedge rst_n)

if (!rst_n)

begin

data_a <= 'b0;

addr_a <= 'b0;

data_b <= 'b0;

addr_b <= 'b0;

end

else if (wr_a)

begin

data_a <= idin;

addr_a <= addr_a + 1'b1;

end

else if (wr_b)

begin

data_b <= idin;

addr_b <= addr_b + 1'b1;

end

dualram ram (

// input

.address_a(addr_a),

.address_b(addr_b),

.clock(clk),

.data_a(data_a),

.data_b(data_b),

.wren_a(wr_a),

.wren_b(wr_b),

//output

.q_a(),

.q_b()

);

endmodule

*************************************************************************

module ramtb;

reg clk;

reg rst_n;

reg [7:0] idin;

always #5 clk = ~clk;

initial

begin

#0 clk = 0;

#0 rst_n = 0;

#5 rst_n = 1;

idin = 0;

end

always @ (posedge clk)

idin <= idin + 1;

ram ram_tb (

.clk(clk),

.rst_n(rst_n),

.idin(idin)

);

endmodule

本人有几个疑惑的地方:求高手能给小弟解答一下

1. 初始状态下的写使能该如何确定下来呢?按我这样的写法可以么?

2. 这里我用地址自动计数到31时,在时钟周期到来时控制写使能,在下一时钟周期到来时控制写入数据流的方向。按我这样的写法可以么?

3. 仿真发现只到第31个地址的时候就翻转了,理论上应该到32才翻转的,而且地址怎么过了15之后就出现负值了, 这个很奇怪。

module ram ( clk, rst_n, idin);

input clk;

input rst_n;

input [7:0] idin;

reg wr_a , wr_b;

reg [4:0] addr_a, addr_b;

reg [7:0] data_a, data_b;

wire a ,b;

assign a = addr_a == 'b1_1111 ? 1 : 0;

assign b = addr_b == 'b1_1111 ? 1 : 0;

always @ (posedge clk or negedge rst_n)

if (!rst_n)

begin

wr_a <= 1'b1;

wr_b <= 1'b0;

end

else if (a)

begin

wr_a <= 1'b0;

wr_b <= 1'b1;

end

else if (b)

begin

wr_a <= 1'b1;

wr_b <= 1'b0;

end

always @ (posedge clk or negedge rst_n)

if (!rst_n)

begin

data_a <= 'b0;

addr_a <= 'b0;

data_b <= 'b0;

addr_b <= 'b0;

end

else if (wr_a)

begin

data_a <= idin;

addr_a <= addr_a + 1'b1;

end

else if (wr_b)

begin

data_b <= idin;

addr_b <= addr_b + 1'b1;

end

dualram ram (

// input

.address_a(addr_a),

.address_b(addr_b),

.clock(clk),

.data_a(data_a),

.data_b(data_b),

.wren_a(wr_a),

.wren_b(wr_b),

//output

.q_a(),

.q_b()

);

endmodule

*************************************************************************

module ramtb;

reg clk;

reg rst_n;

reg [7:0] idin;

always #5 clk = ~clk;

initial

begin

#0 clk = 0;

#0 rst_n = 0;

#5 rst_n = 1;

idin = 0;

end

always @ (posedge clk)

idin <= idin + 1;

ram ram_tb (

.clk(clk),

.rst_n(rst_n),

.idin(idin)

);

endmodule

3.32个数是0~31而不是1~32.你选择的现实模式有错,选择无符号十进制显示就行了

谢谢了,第三个问题解决了。

最大的问题是如何能让此程序写A的时候读B, 写B读A 呢?