Verilog 輸出高阻抗 求解

时间:10-02

整理:3721RD

点击:

小弟目前在做

Mips single cycle的TOP module下的submodule之間的連接

現在初步要連PC和IM

連接完成後

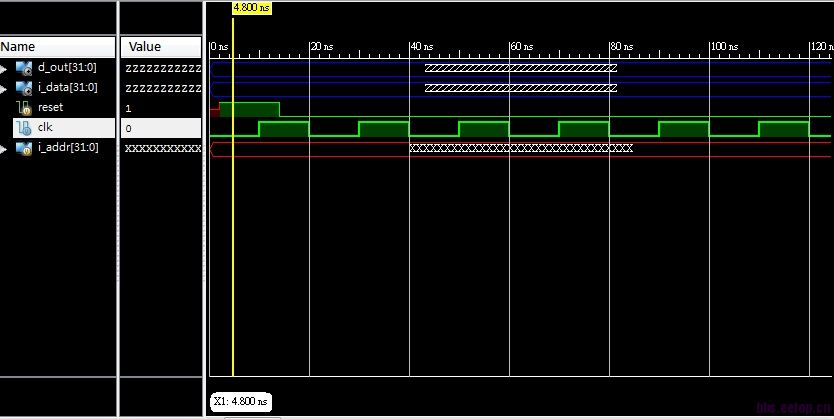

波型圖上的PC端輸出 (d_out[31:0]) 怎麼都是高阻抗,

小弟困擾好多天了,麻煩各位大俠幫幫忙了..

這是top module code*********************

- `timescale 1ns / 1ps

- module TOP(reset,clk);

- input reset,clk;

- wire [31:0] d_out_i_addr;

- wire [31:0] i_data;

- PC mips_PC (

- .clk(clk),

- .reset(reset),

- .d_out(d_out_i_addr)

- );

- IM mips_IM (

- .clk(clk),

- .i_addr(d_out_i_addr),

- .i_data(i_data)

- );

- endmodule

這是 pc code************************

-

- `timescale 1ns / 1ps

- module PC(clk, reset, d_out);

- input clk, reset;

-

- output [31:0] d_out;

- reg [31:0] d_out;

-

- always @(posedge clk)

- begin

- if (reset==1'b1)

- d_out <= 0;

- else

- d_out = d_out+4;

- end

- endmodule

IM code*********************************

-

- `timescale 1ns/100ps

- module IM(

- clk, // input clock

- i_addr, // input address

- i_data // output data

- );

- // parameter declaration

- parameter P_BITS = 32;

- parameter P_WORD_DEPTH = 256;

- parameter P_ADDR_WIDTH = 32;

- parameter P_DELAY = 1.6;

-

- //input,output declaration

- input clk; // input clock

- input [P_ADDR_WIDTH - 1:0] i_addr; // input address

- output [P_BITS - 1:0] i_data; // output data

- // registers declaration

- reg [P_BITS - 1:0] i_data; // output data

- reg [8:0] index; // for initialization

- // (128M)*32 memory

- reg [P_BITS - 1:0] mem [0:P_WORD_DEPTH - 1]; // define memory

-

- // initialize memory value

- initial begin

- for(index = 9'b0; index < P_WORD_DEPTH; index = index + 9'b1)

- mem[index] = 8'b0;

-

- // load instruction

- $readmemh("pattern.txt", mem);

- end

- // function definition

- always@(posedge clk) begin :memaccess_proc

- i_data <= #P_DELAY mem[i_addr[9:2]];

- end // end memaccess_proc

- endmodule

Topmodule Testbench*****************************

-

- `timescale 1ns / 1ps

-

- module TOP_test;

- // Inputs

- reg reset;

- reg clk;

-

-

- reg [31:0] i_addr;//IM in

-

- //outputs

- wire [31:0] d_out; //pc out

- wire [31:0] i_data;//im out

-

- // Instantiate the Unit Under Test (UUT)

- TOP mips_top (

- .reset(reset),

- .clk(clk)

- );

-

- always #10//5ns, clock1從1->0 or 0->1, clock period 10ns

- begin

- clk=~clk;

- end

- initial begin

- // Initialize Inputs

- clk=0;

- #2 reset=1;

- #12 reset=0;

- // Wait 100 ns for global reset to finish

- #100;

-

- // Add stimulus here

- end

-

- initial

- begin

- $dumpfile("TOP_test_go.fsdb");

- $dumpvars;

- end

- endmodule

Isim

module TOP_test;

// Inputs

reg reset;

reg clk;

reg [31:0] i_addr;//IM in

//outputs

wire [31:0] d_out; //pc out

wire [31:0] i_data;//im out

d_out, i_data是top_test里面的,根本没有被赋值,当然是高阻或者X。

层次都搞不清楚。