Verilog中`include"*.v"问题求解

时间:10-02

整理:3721RD

点击:

源程序为:

文件一:

module flop(data,clock,clear,q,qb);

input data,clock,clear;

output q,qb;

nand #10 nd1(a,data,clock,clear),

nd2(b,ndata,clock),

nd4(d,c,b,clear),

nd5(e,c,nclock),

nd6(f,d,nclock),

nd8(qb,q,f,clear);

nand #9 nd3(c,a,d),

nd7(q,e,qb);

not #10 iv1(ndata,data),

iv2(nclock,clock);

endmodule

文件二:

`include "flop.v"

module hardreg(d,clk,clrb,q);

input clk,clrb;

input[3:0] d;

output[3:0] q;

flop f1(d[0],clk,clrb,q[0],),

f2(d[1],clk,clrb,q[1],),

f3(d[2],clk,clrb,q[2],),

f4(d[3],clk,clrb,q[3],);

endmodule

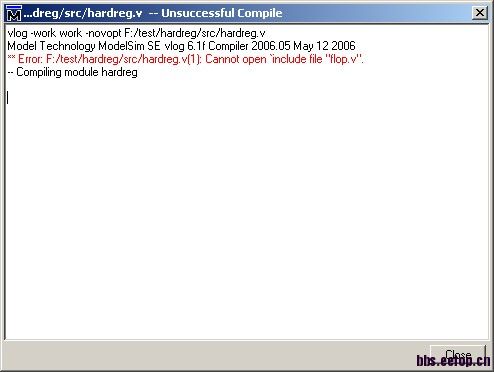

像这种打开子文件的代码试了好多,但是在ModelSim中编译时老是报错

求解

文件一:

module flop(data,clock,clear,q,qb);

input data,clock,clear;

output q,qb;

nand #10 nd1(a,data,clock,clear),

nd2(b,ndata,clock),

nd4(d,c,b,clear),

nd5(e,c,nclock),

nd6(f,d,nclock),

nd8(qb,q,f,clear);

nand #9 nd3(c,a,d),

nd7(q,e,qb);

not #10 iv1(ndata,data),

iv2(nclock,clock);

endmodule

文件二:

`include "flop.v"

module hardreg(d,clk,clrb,q);

input clk,clrb;

input[3:0] d;

output[3:0] q;

flop f1(d[0],clk,clrb,q[0],),

f2(d[1],clk,clrb,q[1],),

f3(d[2],clk,clrb,q[2],),

f4(d[3],clk,clrb,q[3],);

endmodule

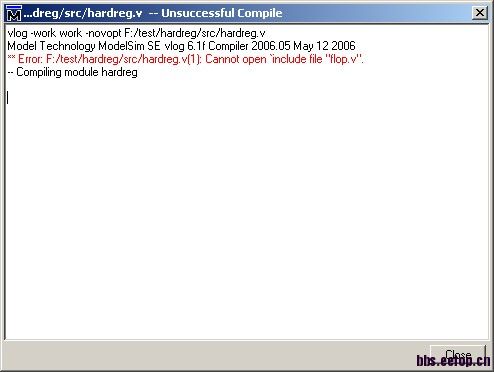

像这种打开子文件的代码试了好多,但是在ModelSim中编译时老是报错

求解

用绝对路径试试。

+incdir+your_file_included_path

其中,your_file_included_path,就是`include "aaaa.v"中的aaaa.v所在path。

恩!已经解决,必须把`include"*.v"中*.v文件与所建工程放到同一路径。

多谢指点