晶振输入作内部时钟

时间:10-02

整理:3721RD

点击:

我用晶振输入直接作为内部时钟,编译后timequest里面好多红色,具体还看不懂是什么意思。但是,标红的有输入时钟和PLL(用输入时钟做倍频)。

请问,这样是不是晶振时钟波形不好导致的,需要怎么处理?看到有人说用buff,不知道该如何用,请大家指点一下。

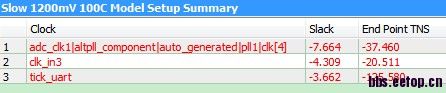

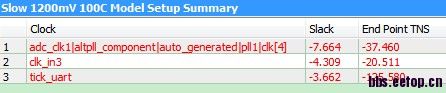

打开这些标红项后,基本都是涉及到三个信号:晶振时钟、通过PLL倍频后的400MHz时钟(其它的是200MHz)、一个内部生成的时钟。

比如:

clk_in3是输入时钟 --50MHz

adc_clk1是PLL的例化名,clk[4]应该是倍频后的400MHz时钟

tick_uart是内部产生的时钟(这样做不好,但是目前没想到好办法)

请大家帮忙分析一下clk[4]和clk_in3的时序问题是什么原因造成的,谢谢!

请问,这样是不是晶振时钟波形不好导致的,需要怎么处理?看到有人说用buff,不知道该如何用,请大家指点一下。

不是太清楚你说的红色信息具体有什么,不过在板子上可以将晶振的输出通过一个clockbuffer进行整形,或者在FPGA内部加一个PLL处理一下,这样也许能解决你的问题。

小弟第一个FPGA的板子,正在设计,项目用器件为ALTERA 的 EP3C25。

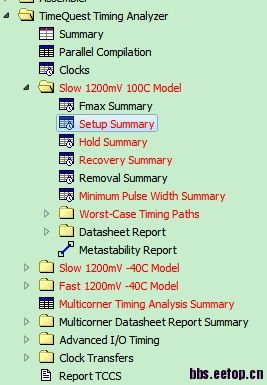

编译报告如下:

打开这些标红项后,基本都是涉及到三个信号:晶振时钟、通过PLL倍频后的400MHz时钟(其它的是200MHz)、一个内部生成的时钟。

比如:

clk_in3是输入时钟 --50MHz

adc_clk1是PLL的例化名,clk[4]应该是倍频后的400MHz时钟

tick_uart是内部产生的时钟(这样做不好,但是目前没想到好办法)

请大家帮忙分析一下clk[4]和clk_in3的时序问题是什么原因造成的,谢谢!

器件等级太低 跑不到400M

没啥问题,是你的设计跑不到400M而已

楼上两位,是器件跑不到还是设计有问题?我选的是I7等级。

另外,还有两个问题:

1. 我用这个时钟对AD数据进行操作,恢复后的波形是正确的,只是有不到5%的误码。为什么呢?

2. 这面提到的50MHz晶振时钟为什么也有问题呢?