请问这种延时该如何处理掉呢?

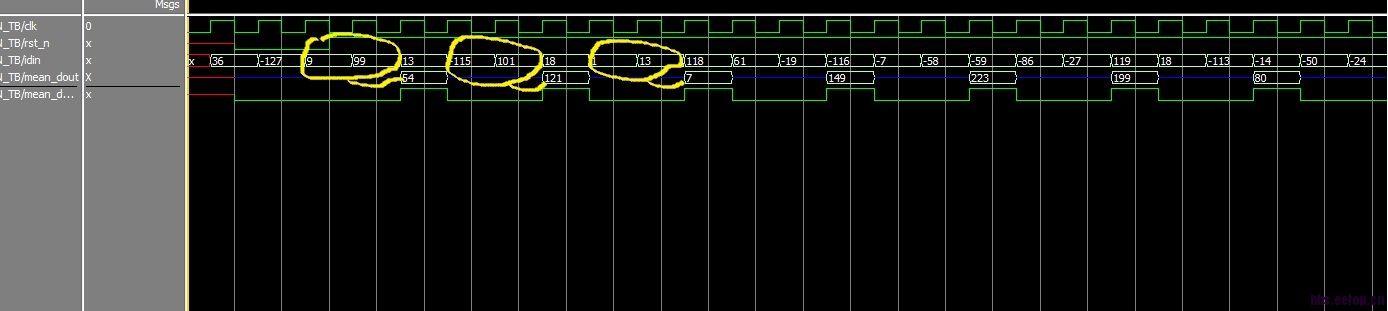

这里编写了一个求平均数的程序,每输入两个数求一次平均数。但这样写的话平均数输出是在每第三个输入周期,

这样当第三个周期来的时候,新的数据就浪费掉了。怎样改才能保证每两个周期就正好输出一个平均值呢?

module MEAN (

clk,

rst_n,

idin,

mean_dout,

mean_done

);

input clk;

input rst_n;

input [7:0] idin;

output [63:0] mean_dout;

output mean_done;

wire clk, rst_n;

wire [7:0] idin;

wire [63:0] mean_dout;

wire [63:0] buf_mean;

wire mean_done;

reg [9:0] size;

reg [7:0] buf_idin;

reg [63:0] buf_sum;

assign mean_dout = buf_mean;

assign mean_done = (size == 2'b10)? 1 : 0;

assign buf_mean = (mean_done == 1) ? buf_sum >>1 : 'hz;

always @ (posedge clk or negedge rst_n)

if (!rst_n)

begin

buf_idin = 'b0;

buf_sum = 'b0;

size = 'b0;

end

else if (!mean_done)

begin

size = size + 1'b1;

buf_idin = idin;

buf_sum = buf_sum + buf_idin;

end

else if (mean_done)

begin

buf_idin = 'b0;

size = 'b0;

buf_sum = 'b0;

end

endmodule

module MEAN(

clk,

rst_n,

idin,

mean_dout,

mean_done

);

input clk,rst_n;

input [7:0] idin;

output [7:0] mean_dout;

output mean_done;

reg [7:0] idin_d1;

wire [8:0] sum;

reg rdone;

assign sum=idin_d1+idin;

assign mean_dout=sum[8:1];

assign mean_done=~rdone;

always @(posedge clk,negedge rst_n)

if(!rst_n)

begin

idin_d1<=8'd0;

rdone<=1'b0;

end

else

begin

idin_d1<=idin;

rdone<=~rdone;

end

endmodule

没有仿真,不能保证正确。可以参考一下。

更正一下,下面的程序应该是正确的了。

module MEAN(

clk,

rst_n,

idin,

mean_dout,

mean_done

);

input clk,rst_n;

input [7:0] idin;

output [7:0] mean_dout;

output mean_done;

reg [7:0] idin_d1;

reg [8:0] sum;

reg rdone;

assign mean_dout=sum[8:1];

assign mean_done=~rdone;

always @(posedge clk,negedge rst_n)

if(!rst_n)

begin

idin_d1<=8'd0;

rdone<=1'b0;

sum<=9'd0;

end

else

begin

idin_d1<=idin;

sum<=idin_d1+idin;

rdone<=~rdone;

end

endmodule