請教verilog問題

假設一個訊號叫DPI

一開始的DPI是1 接著為0 ,在變1又回到0=> 1->0->1->0 =>給charge_EN

當我到最後一個0的時候要給一個電壓叫做charge_EN

請問該怎麼寫呢 是不是需要counter數兩次再給 麻煩版上大哥大姊們不吝教學一下

就是说检测到DPI连续两次从1到0才会产生charge_en信号?要是这样,用计数器应该可以的。但是也要取决于DPI后面的变化,如果接下来还是一次1到0的变化,你是马上产生还是等待两次以后产生?

使用计数器 是一种 比较好的方式

給了charge_EN之後

DPI後面的直就維持在charge_EN 不會再改變

這樣該如何寫呢

你这种描述方式实在难以看懂。有条件画个时序图可好

如果用计数器的话可能会出现1=>0=>0=>1=>0时(也就是没有连续出现下降沿)也会有en信号。

建议用状态机来实现。

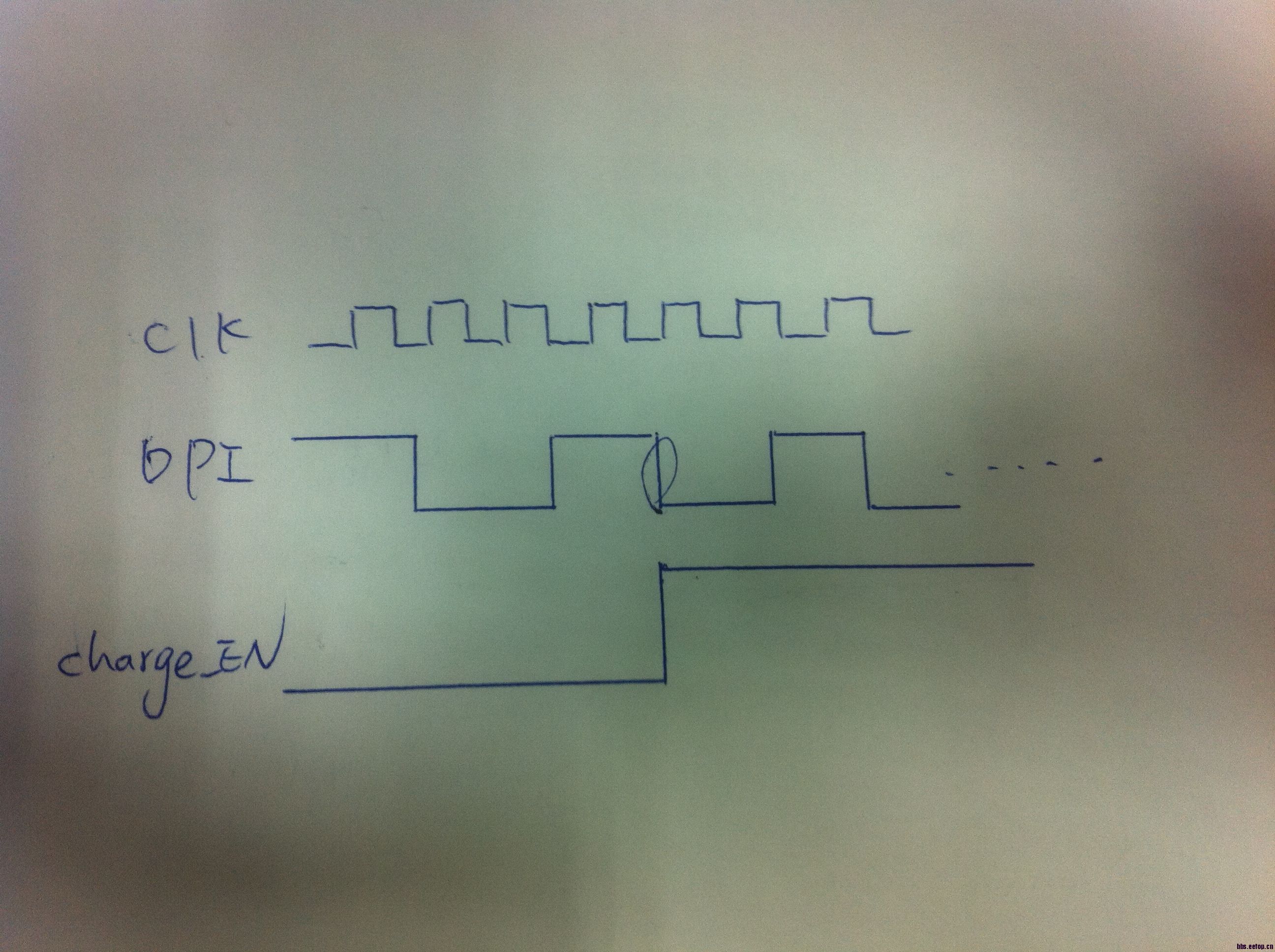

我大概畫了一下簡單的波形

在DPI第二次為0的時候給charge_EN

不管DPI後面如何變化 charge_EN永遠為1

代码有问题

不好意思 我剛剛的clk沒畫的很好

重畫一次拍起來

建议用FSM。

比较好控制、修改。

/////Just for you test

reg dpi_d1, dpi_d2, dpi_d3;

always @(negedge rstb or posedge clk)

begin

if(!rstb)

{dpi_d3, dpi_d2, dpi_d1} <= 3'b000;

else

{dpi_d3, dpi_d2, dpi_d1} <= {dpi_d2, dpi_d1, DPI};

end

wire dpi_negedge = ~dpi_d2 & dpi_d3;

reg [1:0] cnt;

always @(negedge rstb or posedge clk)

begin

if(!rstb)

cnt <= 2'h0;

else if((cnt<2'h2) && dpi_negedge)

cnt <= cnt + 2'h1;

end

reg CHARGE_EN;

always @(negedge rstb or posedge clk)

begin

if(!rstb)

CHARGE_EN <= 1'b0;

else if(cnt>= 2'h2)

CHARGE_EN <= 1'b1;

end

謝謝各位大大 我會參考學習的~

提供另一种省面积的方法:

首先,将DPI信号2分频:

reg div2_dpi;

always @(negedge DPI or negedge rstn)

if(~rstn)

div2_dpi <= 1'b0;

else

div2_dpi <= ~div2_dpi;

然后,使用2分频后信号的下降沿作为触发条件,产生需要的信号,也可以使用latch锁存数据:

reg change_en_r1;

always @(negedge div2_dpi or negedge rstn)

if(~rstn)

change_en_r1 <= 1'b0;

else

change_en_r1 <= 1'b1;

最后,最好再使用主时钟同步2次,消除亚稳态的影响:

reg change_en_r2;

reg change_en;

always @(negedge DPI or negedge rstn)

if(~rstn)

begin

change_en_r2 <= 1'b0;

change_en <= 1'b0;

end

else

begin

change_en_r2 <= change_en_r1;

change_en <= change_en_r2;

end

一个计数器从0到5计数,DPI就是这个计数器除以2得到的余数?