关于流水线设计的加法器输出异常,有问题请教大家。

功能仿真么有问题,但是时序仿真最后出了问题,本来一个上升沿对应一个输出,结果却是一个上升沿产生了多个输出。

截图如下:

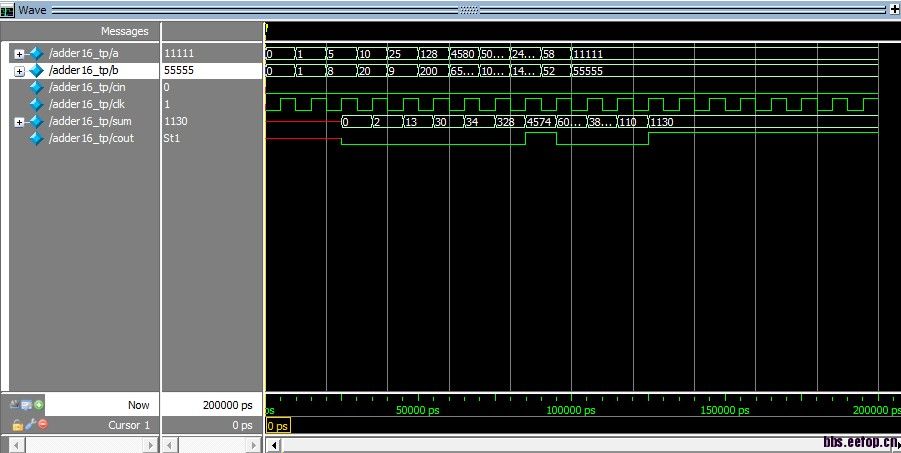

功能仿真(正确)

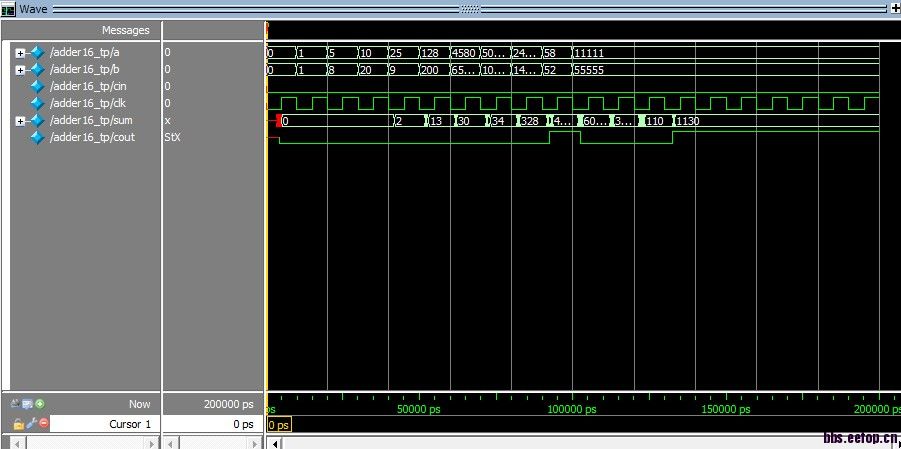

时序仿真(出错误了)

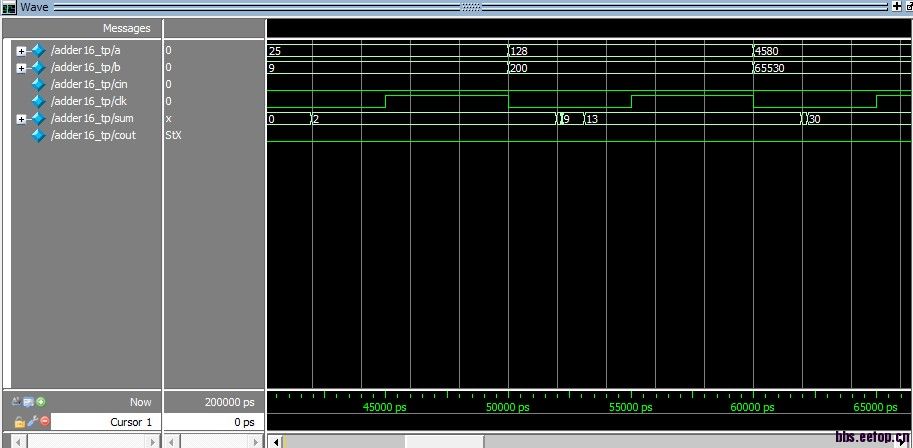

比如最后一幅图中,13的那个结果是正确的,但是前面又多出了好几个结果,不知道怎么来。

程序附上

模块代码:

- module adder16(a,b,cin,clk,sum,cout);

- input[15:0] a,b;

- input cin;

- input clk;

- output[15:0] sum;

- output cout;

- reg[15:0] sum;

- reg cout;

- reg[15:0] temp_a,temp_b;

- reg temp_cin;

- reg[7:0] first_sum;

- reg first_cout;

- reg[7:0] first_a,first_b;

- always @(posedge clk)

- begin

- temp_a<=a;temp_b<=b;temp_cin<=cin;

- end

- always @(posedge clk)

- begin

- {first_cout,first_sum}<={1'b0,temp_a[7:0]}+{1'b0,temp_b[7:0]}+temp_cin;

- first_a<=temp_a[15:8];

- first_b<=temp_b[15:8];

- end

- always @(posedge clk)

- begin

- {cout,sum}<={first_a,8'b0}+{first_b,8'b0}+{first_cout,first_sum};

- end

- endmodule

激励代码:

- `timescale 1ns/1ns

- module adder16_tp;

- wire[15:0] sum;

- wire cout;

- reg[15:0] a,b;

- reg cin,clk;

- parameter cycle=10;

- adder16 my_adder16(a,b,cin,clk,sum,cout);

- always #(cycle/2) clk=~clk;

- initial

- begin

- clk=0;a=0;b=0;cin=0;

- #cycle a=1;b=1;

- #cycle a=5;b=8;

- #cycle a=10;b=20;

- #cycle a=25;b=9;

- #cycle a=128;b=200;

- #cycle a=4580;b=65530;

- #cycle a=50000;b=10000;

- #cycle a=24254;b=14242;

- #cycle a=58;b=52;

- #cycle a=11111;b=55555;

- #(cycle*10) $stop;

- end

- endmodule

你说的应该就是后仿吧,这个是因为组合逻辑到达寄存器的时间不同造成的,是正常的。

只要时序满足setup时间就没有问题

请教怎么知道时序是否满足steup时间,我用的是quartus II。

不是说后仿是最接近实际的吗?

不知道这个结果对不对?

毛刺而已,计算结果各bit到达寄存器时间不同导致的,使用结果的时候用寄存器锁一拍再用。

ripple问题,transition的时间不同造成的

稳定后的信号是正确值。带时序的仿真应该是正确的。

如果你还不知道是否满足setup,说明你还有许多要学习的。

QUARTUS中有没有对时钟频率进行约束?

请教是用D触发器吗?

steup时间是不是和器件有关系?

我是菜鸟,有很多东西还不熟悉,请多指教。

ripple问题,transition的时间不同造成的

是D触发器

用quartus仿真是带了器件的延时的

setup time 是说FF的clk和data之间的时序约束 不同的cell 不一样

但是你现在用的是100MHz的时钟啊! 你的输出都已经在时钟的下降沿之后了

你可以试试把时钟频率改的慢一些 再仿真看看!

一般寄存器都指D触发器。

出现这种情况是正常的,通常我们把它称为毛刺。毛刺可以减少但不能避免,可以考虑加D触发器来减少毛刺。

1、在RTL级仿真时,如果没有加入延迟参数的话,那么仿真器默认的线延迟(wire delay)和单元延迟(cell delay)都是为0的,所以你会看到信号在同一时间点变化。

2、在Gate级仿真时,反标了标准延迟文件(.sdf),此时线(wire)和单元(cell)都包含了延迟信息,所以你会看到信号的变化不在同一个时间点,就出现了毛刺(glitch)。

只要在你取样数据前(当然要满足setup time),该数据是正确的就可以了,不管它在期间有多少错误数据,都无所谓的。另外,需要指出的是,时序电路有两种情况:single-cycle clock和multi-cycle clock

另外提一下,第二级流水线代码写的有问题,最好如下:

//second level pipe-line

always @(posedge clk)

begin

{cout,sum[15:8]} <= {1'b0,first_a}+{1'b0,first_b}+{7'b0,first_cout};

sum[7:0] <= first_sum;

end