pll时序如何用timequest处理

时间:10-02

整理:3721RD

点击:

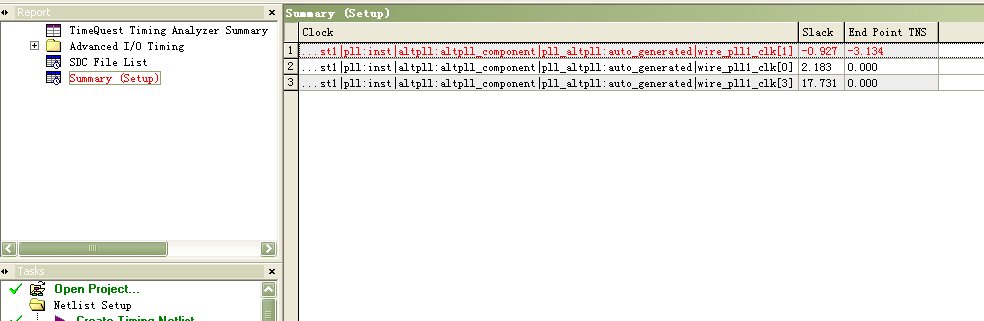

这张图是我工程编译以后的timequest中的setup的报告

我已经约束了输入时钟clk 和pll

sdc文件中已添加的代码如下:

create_clock -name {sysclk} -period 41.660 -waveform { 0.000 20.830 } [get_ports {CLK}]

#**************************************************************

# Create Generated Clock

#**************************************************************

derive_pll_clocks -use_tan_name

但还出现了附件图片中的问题

clk1按照设计要求 未给任何偏移量

请大侠们指教下 下面要怎么处理 才能让clk[1]的slack为正?

我已经约束了输入时钟clk 和pll

sdc文件中已添加的代码如下:

create_clock -name {sysclk} -period 41.660 -waveform { 0.000 20.830 } [get_ports {CLK}]

#**************************************************************

# Create Generated Clock

#**************************************************************

derive_pll_clocks -use_tan_name

但还出现了附件图片中的问题

clk1按照设计要求 未给任何偏移量

请大侠们指教下 下面要怎么处理 才能让clk[1]的slack为正?

slack出现负的话就一定无法通过时序要求吗?

PLL生成的时钟之间有没有关联性。有的话可以用set_multicycle_path 试试!

如果是时钟之间没有关联性的话,直接设置成false_path就可以了,timequest就不会分析了

Timequest默认是把设计中的所有时钟当成有关系的,如果两个时钟域间没有数据传递,是需要自己把路径剪除掉的。

写sdc的时候,有以下严重警告:

Critical Warning: From altera_reserved_tck (Rise) to altera_reserved_tck (Rise) (setup and hold)

怎么解决呢