quartusii 9.1sp2到modelsim-altera 6.5b 的仿真

时间:10-02

整理:3721RD

点击:

VHDL的设计文件如下:(就是一个最简单的分频器)

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use ieee.std_logic_unsigned.all;

entity fenpin is

generic (DWIDTH: integer:=3);

port(

clk:in std_logic;

en: in std_logic;

clk_out: out std_logic

);

end fenpin;

architecture rtl of fenpin is

signal temp: std_logic_vector(DWIDTh-1 downto 0);

begin

process(clk,en)

begin

if en='1' then

if clk'event and clk='1' then

temp<=temp+'1';

else

NULL;

end if;

end if;

end process;

clk_out<=temp(DWIDTH-1);

end rtl;

-------------------------------------------

testbench如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY fenpin_vhd_tst IS

END fenpin_vhd_tst;

ARCHITECTURE fenpin_arch OF fenpin_vhd_tst IS

SIGNAL clk : STD_LOGIC:='0';

SIGNAL clk_out : STD_LOGIC;

SIGNAL en : STD_LOGIC:='1';

COMPONENT fenpin

PORT (

clk : IN STD_LOGIC;

clk_out : OUT STD_LOGIC;

en : IN STD_LOGIC

);

END COMPONENT;

BEGIN

i1 : fenpin

PORT MAP

(

clk => clk,

clk_out => clk_out,

en => en

);

PROCESS

BEGIN

wait for 10 ns;

clk<='1';

wait for 10 ns;

clk<='0';

END PROCESS;

END fenpin_arch;

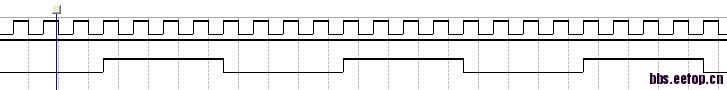

点了EDA RTL simulation后出来moderlsim界面,然后点击run 1us后出现全是红线,不知道怎么回事啊?

modelsim就是红线

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use ieee.std_logic_unsigned.all;

entity fenpin is

generic (DWIDTH: integer:=3);

port(

clk:in std_logic;

en: in std_logic;

clk_out: out std_logic

);

end fenpin;

architecture rtl of fenpin is

signal temp: std_logic_vector(DWIDTh-1 downto 0);

begin

process(clk,en)

begin

if en='1' then

if clk'event and clk='1' then

temp<=temp+'1';

else

NULL;

end if;

end if;

end process;

clk_out<=temp(DWIDTH-1);

end rtl;

-------------------------------------------

testbench如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY fenpin_vhd_tst IS

END fenpin_vhd_tst;

ARCHITECTURE fenpin_arch OF fenpin_vhd_tst IS

SIGNAL clk : STD_LOGIC:='0';

SIGNAL clk_out : STD_LOGIC;

SIGNAL en : STD_LOGIC:='1';

COMPONENT fenpin

PORT (

clk : IN STD_LOGIC;

clk_out : OUT STD_LOGIC;

en : IN STD_LOGIC

);

END COMPONENT;

BEGIN

i1 : fenpin

PORT MAP

(

clk => clk,

clk_out => clk_out,

en => en

);

PROCESS

BEGIN

wait for 10 ns;

clk<='1';

wait for 10 ns;

clk<='0';

END PROCESS;

END fenpin_arch;

点了EDA RTL simulation后出来moderlsim界面,然后点击run 1us后出现全是红线,不知道怎么回事啊?

求高手啊~

temp复位给个初始值看看。

我用ISE调用modelsim也是这问题,单独用modelsim仿真没问题。搞了好久都没弄好

现在只好分开用,先用modelsim仿真,验证了以后再用ISE做后续的。

要赋初值

quartus里仿真是行的

modelsim就是红线