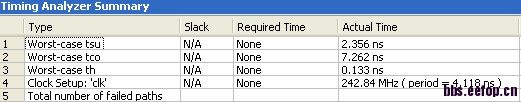

为什么tco都7ns了,综合结果显示时钟还可以跑到200多M?

如图显示,建立时间为2ns多,但是tco,也就是D触发器时间为7ns多,这样加起来就有9ns多了,为什么时钟还可以跑到200多M

PS:他显示的是clock setup:"clk",难道是只针对建立时间?这样有什么意义呢?那我要查看实际时钟在哪能看到呢

Tco是时钟到输出的时延,不是内部两个寄存器之间的,所以时钟跑多少M与输出时延没有什么必然的关系。

应该是以setup跟hold 为准

时钟周期应该大于关键路径的最大延时,关键路径的延时来源于该级D触发器和该级的组合逻辑电路长度吧。所以时钟周期T应该大于Tco(D触发器时钟到输出延时)+Tcomb(组合逻辑延时),即T>Tco+Tcomb。

在FPGA设计中,时钟周期一般都只考虑建立时间,保持时间一般都可做忽略吧。这样的话,那Tsu=Tco+Tcomb吧。

恩,确实是以建立和保持时间来参考,但是建立时间是以Tco和Tcomb来参考啊。

Tco是指时钟到输出的延时,这个应该是指D触发器的时钟到输出的延时吧。

好像我记得,最快周期应该是 PERIOD = TSU + Tco (THD+ Tcomb . 从时钟到输出的时间里边包含了保持时间。

需要认证一下。呵呵。

刚看了下http://wenku.baidu.com/view/af2f012458fb770bf78a5564.html

觉得写的很好

按照这个逻辑,那时钟大小就与Tsu、Tcomb、Tco都有关系,所以我就更搞不懂quartus那张图了

按理说T>=setup+tco+com的吧 不明白这张图

我猜

这个TCO是最后输出的地方,小编的模块输出是组合逻辑输出,到FPGA外面,所以TCO很大,但又不影响内部的timing...

同意LS,还有个因素,可能LZ没有做PIN脚的时序分析,所以报不出来。

我也在想这个TCO是不是就是指最后一级,也就是输出端口的寄存问题,但是即便是最后一级输出端口的寄存,时钟周期也不能小于这个TCO吧,不然数据还出错呀

这个我到没有想到,想请问PIN脚的时序分析怎么做呀,求指教

我觉得worst Tco是最后一级寄存器到外部pin的延时,内部的Tco不会有这么大的,最大时钟应该是内部始终最大值,没有考虑IO上的延时。一般来说IO的延时都有3~5ns,pin上的Tco肯定是worst的

Quartus II 还是用TimeQuest Timing Analyzer吧。

port上的约束,dc中的set_input_delay, set_output_delay吧,在fpga上就不清楚了,应该有相对应的吧

就像9楼说的,组合逻辑会影响时序分析的,你建个纯组合逻辑工程跑跑就知道了。在输出口附件放个D触发器打一下,再来跑就能知道准确的了

恩,这个说得在理,但是还是就是那个问题,即使是i输出到pin脚的延时,时钟周期也还是得满足他吧,不然也会有问题呀

他的工具可能不考虑到输出pin上的延时,因为去外部pin上的东西,外面怎么用工具也不知道,可能就把他的延时忽略了。