关于产生时钟的问题

时间:10-02

整理:3721RD

点击:

module clkdiv(

input clk,

output reg clkdiv

);

initial begin clkdiv <= 0;end

always @ (posedge clk)

begin

clkdiv <= ~clkdiv;

end

endmodule

input clk,

output reg clkdiv

);

initial begin clkdiv <= 0;end

always @ (posedge clk)

begin

clkdiv <= ~clkdiv;

end

endmodule

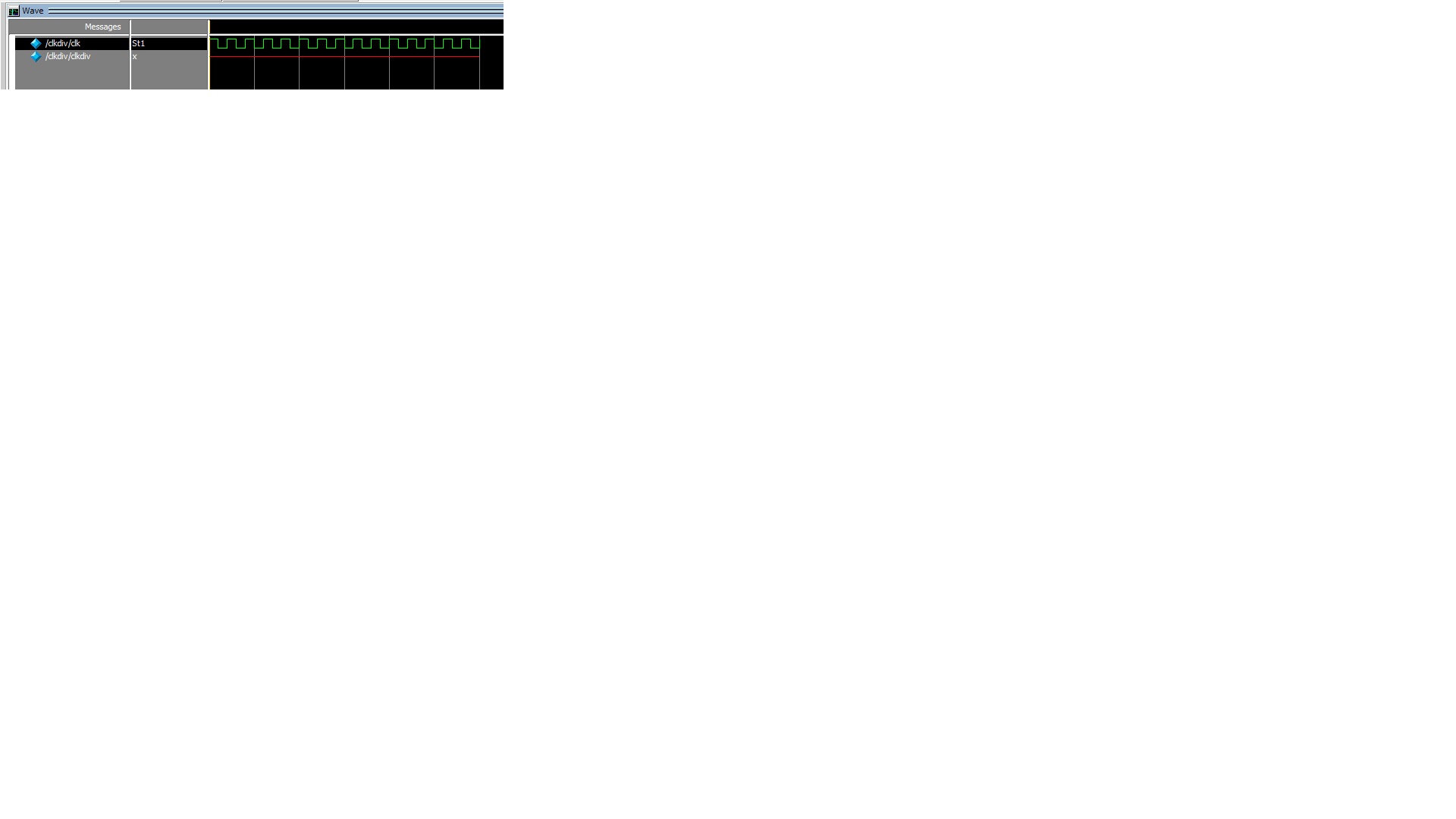

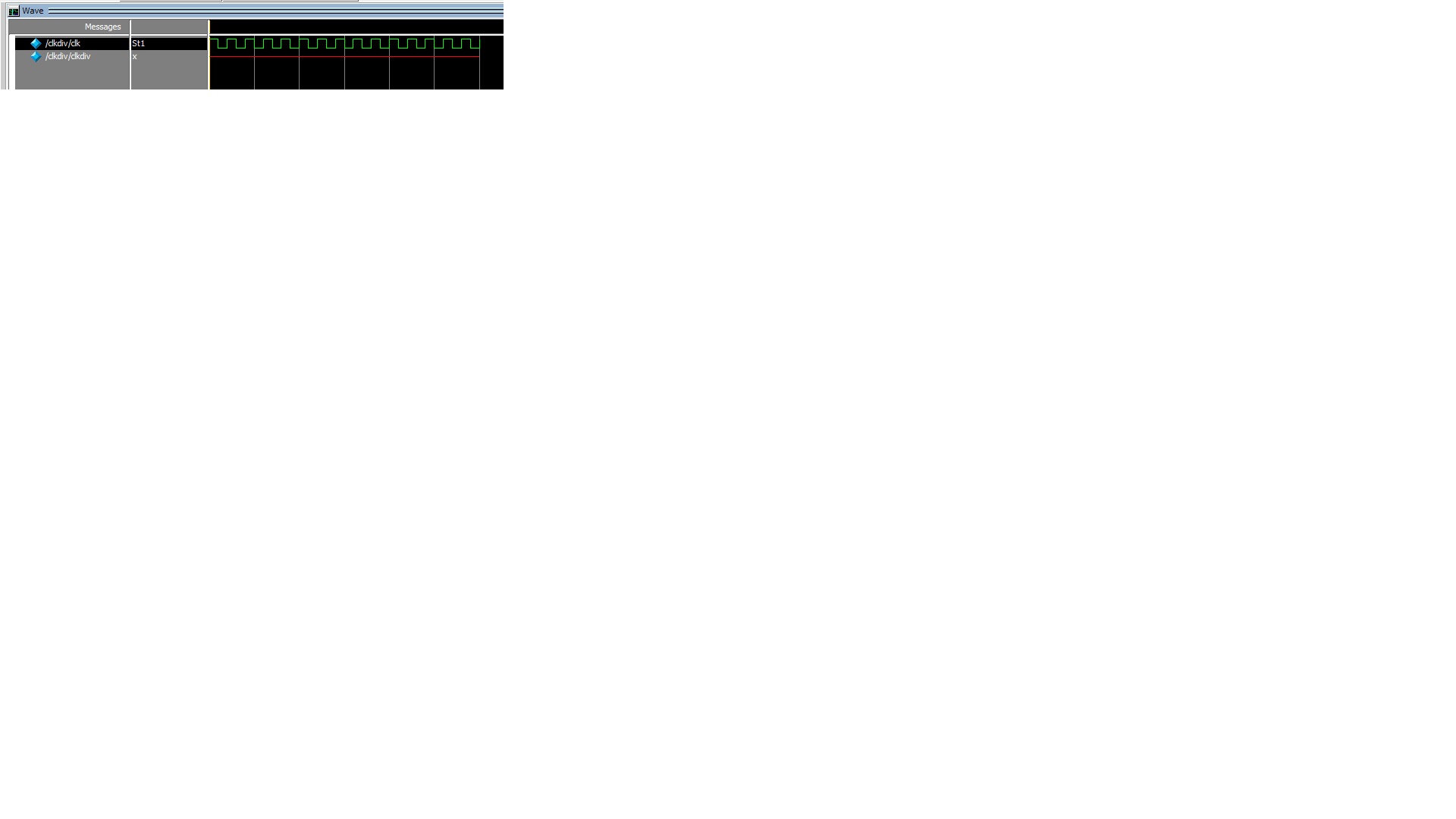

主要是clkdiv信号已经赋初值了,为什么还这样?

initial 里面应该直接用=吧

其实是不需要赋初值的,这里不定态是仿真工具造成的。

仿真工具与实际电路是有区别的。

实际的分频寄存器clkdiv_reg即使没有复位,也会在上电后很快稳定到一个值的0/1。

而仿真工具,却不会这样,会一直将这个不定太延续下去。

你可以再仿真开始,用force clkdiv = 0,一个时钟周期后release clkdiv。

学习了,谢谢啊~

我来逛逛,学学

看来verilog语言还真有意思啊

四楼说的好

你给的波形图最左边是0时刻吗?

如果是的话,问题可能就出在这里。

0时刻,clk=1,也就是clk信号存在一个x->1变化的上升沿,因此clkdiv会取~clkdiv,

这个操作可能会覆盖你对clkdiv赋初值0的操作。

这取决于仿真器。

你试试让0时刻的clk=0,可能就可以了。

学习了,之前跟小编遇到同样的一个问题,后来用了一个reset复位就放出来了。

学习中,force release

应该用一个reset信号给初始值