ISE中如何设置PAD 到 PAD的MIN DELAY?

时间:10-02

整理:3721RD

点击:

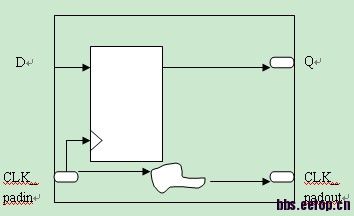

请问,怎么设置从clk_padin到clk_padout的buf的逻辑延迟。想设置为最小5ns,但是ise里面只有MAXDELAY这个设置,没有MINDELAY的

约束,该如何约束呢?

我是这样设置:

NET “CLK_padin" TNM PADS "CLK_padin"

NET “CLK_padout" TNM PADS "CLK_padout"

TIMESPECT "TS_MINDELAY" FROM "CLK_padin" TO "CLK_padout" 5ns

但是,软件的PR出来的delay还是为4.5ns,并没有变成5ns。可能这个约束只是设置最大delay?

该如何设置呢?

ise 既然没有与MAXDELAY对应的MINDELAY的约束,真实无语了。

大侠出点招吧。谢谢。

MINDELAY是有的吧?

不过只能约束一条线的的约束

看你的图不是一条线吧

输入输出时钟线如果是经过DCM之类的,最好查看下DCM的手册,总过线路延迟不能超过5ns,那么MINDELAY的话,两端都需要做更小约束吧。

建议在输出管脚上增加ODELAY单元,通过调整ODELAY的TAP数来控制延迟。在参考时钟为200MHz的情况下, 1 tap的延迟大概是78皮秒。需要多少延迟可以通过约束这个ODELAY的TAP数值来得到。

详细信息参考xilinx对应的FPGA data-sheet和IO使用说明。

我没有做过类似的约束,不过我觉得mindelay主要是修holdtime问题的,而且设定mindelay的代价不小,工具要插入不少垃圾,并且你需要在clock的走线上插入mindelay,更是不好。

你的这个设计我倒建议用前端的方法做,比如clock反相,或者输出的位置插入寄存器。

能在前端做的事情一定不要放给PR来搞,个人建议。