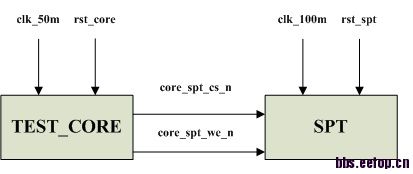

多时钟信号的处理

两个模块之间的信号core_spt_cs_n、core_spt_we_n在处理的时候要注意什么?要不要进行异步处理?

望大家帮忙解答,谢谢了!

理论上不需要,因为是同步电路,而且是慢时钟到快时钟,2倍频。隐约记得是很久以前的虚拟的东东。呵呵。

谢谢你。

这两个模块时钟不一样,怎么是同步电路呢?

你说的意思是不是单个模块是同步电路?

好好去理解一下,什么是同步电路,什么是异步电路。

不是说频率不同就一定不是同步电路。

我也有点模糊 需要去仔细看看 什么是同步电路与异步电路了

同步电路:电路中所有的触发器的时钟端接同一个时钟;否则就是异步电路。

麻烦你给我讲讲,谢谢你了。

看看~

如果一个频率和另一个频率有固定的相位关系,即可称为同步时钟。

如PLL出来的2分频、3分频。等等理论上说是同步的。你那个clk_50m和clk_100m应该是从crg模块产生的,肯定会做成同步的。二分频关系。时钟有很多种,从频率和相位上分。好好找点书籍看看,或问一些有经验的同事。

我觉得,从后端时序分析的角度来说,这些时钟可能认为是同源,当然也取决于互相的相位,时钟延迟,抖动等等。我不确定时序分析工具能否正确的分析这两个时钟域之间的约束。

从前端设计角度来说,应该把跨越这两个时钟之间的信号认为是“跨时钟域(异步)”来处理,这样设计比较保险。当然,我是指从工程角度。如果是做研究(专门优化),或者是对于资源使用非常敏感的话,那要做另外的特殊处理。因为异步时钟处理相对来说比较耗费逻辑。

个人意见,欢迎讨论。

谢谢,果然是牛人

谢谢你的答复,很有道理

综合器不认为你是一棵时钟树下的时钟就不是同步时钟。

在X-FPGA里面,走不同GBUFF的时钟就不是同步的。

即使相位固定,也不能说是同步时钟。

因为相位差要算到时钟倾斜里面去,如果不在一棵时钟树下,综合器就很难得到这个相位差,就很难布线。

不是同步时钟就要异步处理。

如果是ASIC,要流片的,如果clk_50m和clk_100m是同源的,由50m到100m的信号确实不用做同步的,同源时钟在后端做时钟树的时候会进行处理,保证它们的相位关系。当然,你要是硬要同步,如果时序和面积没有太大要求,当然也没有问题了

cs_n在低就使能了,we_n信号你是用低,还是从1到0的triggle?

因为是从低时钟域到高速时钟域,肯定能采得着的,你在快时钟域直接打二拍就可以使用了,

如果是高到慢,且是一个脉冲,那就得注意展宽才使用。

我觉得应该是异步吧,你能保证进入两个模块的时钟一定是两倍关系吗,假如有抖动或者slew不一样呢?

肯定还是要做同步处理的,对于1bit的信号打两拍就好了

上板子验证的时候经常在跨时钟域上出问题

If the 50MHz clock is synchronous to the 100MHz, you do not need to do anything when you design the logic but in your

synthesis/STA constraints, you need to take this synchronization into account.

If the 50MHz clock is asynchronous to the 100MHz, you definitely need to add extra logic to handle the issue caused by clock domain crossing.