求教:多个信号对一个计数器置零的问题。(VHDL)

时间:10-02

整理:3721RD

点击:

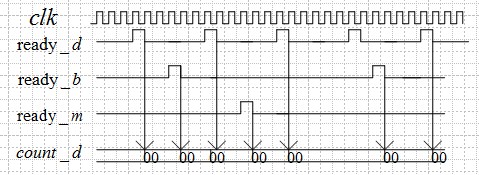

在count_d 计数的过程中,需要多个信号对其置零。具体情况如图所示,我自己编了一下,但综合的时候说不能综合,是个很坏的同步描述。请高手指点一二,这个应该怎么编要好一些呢?

很简单的:

wire clear = ready_d || ready_b || ready_m;

always @(posedge clock) begin

...... 省略reset

if(clear) begin

count_d <= 0;

end

end

谢谢你,可是并不是所有的下降沿都对count_d置零,那又该怎么写代码呢?

哪个下降沿不复位哪个下降沿复位总得有个判断标准吧,从图中没能看出来。

张智星 谢谢 你的资料

就是ready_d的第四个下降沿不复位,其他下降沿都复位。

数到第四个的时候不复位,其他的时候都复位。不就搞定了?再写一个counter嘛。

好的,谢谢。