关于用FPGA语言实现VGA显示彩条仿真老是出不来..求助.内有源程序和仿真截图

时间:10-02

整理:3721RD

点击:

library ieee;

use ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity vga is

port(

reset : in std_logic;

clk : in std_logic;

vga_hs_control : out std_logic;

vga_vs_control : out std_logic;

vga_read_dispaly : out std_logic;

vga_green_dispaly : out std_logic;

vga_blue_dispaly : out std_logic

);

end vga;

ARCHITECTURE a OF vga IS

SIGNAL hs: STD_LOGIC;

SIGNAL vs: STD_LOGIC:='1';

SIGNAL GRB: STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS (clk) --clk = 24MHZ hs = 30 Khz vs = 57hz

VARIABLE i : integer range 0 to 799:=0;

VARIABLE j : integer range 0 to 79:=0;

BEGIN

if reset = '1' then

GRB <= "000"; i:=96; j:=0; hs <= '1';

elsif clk'event and clk = '1' then

if i < 96 then

hs <= '0';

elsif i = 799 then

i:=0;

else

hs <= '1';

end if;

if j = 79 then

GRB(1) <= not GRB(1);

j:=0;

end if;

i:=i+1;

j:=j+1;

end if;

vga_hs_control <= hs;

END PROCESS ;

PROCESS (hs)

VARIABLE k : integer range 0 to 524:=0;

BEGIN

if reset = '1' then

k:=2; vs <= '1';

elsif hs'event and hs = '1' then

if k < 2 then

vs <= '0';

elsif k = 524 then

k:=0;

else

vs <= '1';

end if;

k:=k+1;

end if;

vga_vs_control <= vs;

END PROCESS ;

PROCESS (clk)

BEGIN

if clk'event and clk = '1' and vs = '1' and hs ='1' then

vga_green_dispaly <= GRB(2);

vga_read_dispaly <= GRB(1);

vga_blue_dispaly <= GRB(0);

end if;

END PROCESS ;

END a;

以上是源程序

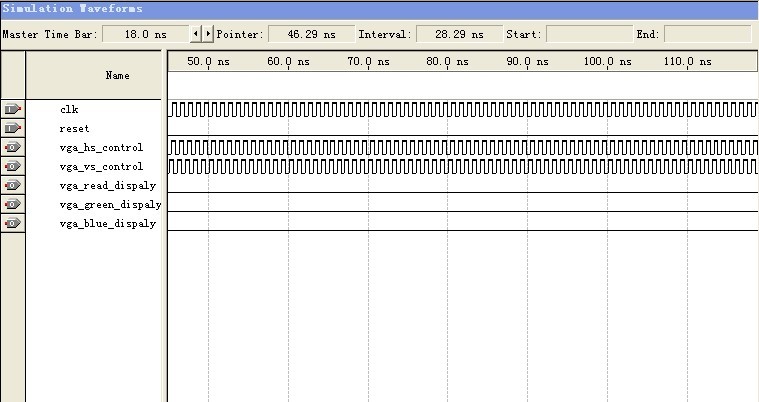

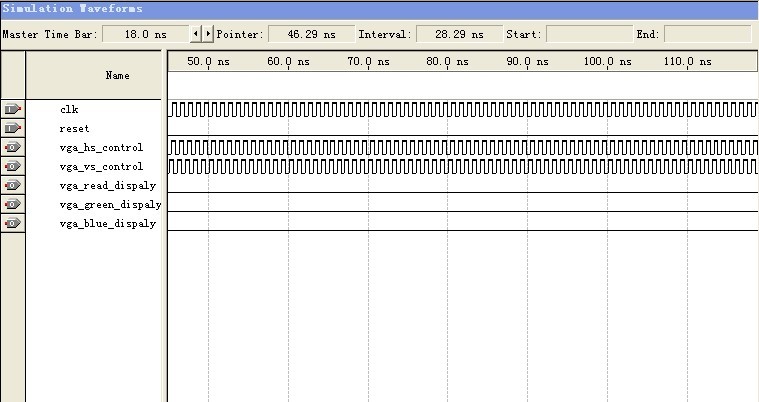

下面是仿真图 RGB 三条输出全部没信号 不知道为什么

use ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity vga is

port(

reset : in std_logic;

clk : in std_logic;

vga_hs_control : out std_logic;

vga_vs_control : out std_logic;

vga_read_dispaly : out std_logic;

vga_green_dispaly : out std_logic;

vga_blue_dispaly : out std_logic

);

end vga;

ARCHITECTURE a OF vga IS

SIGNAL hs: STD_LOGIC;

SIGNAL vs: STD_LOGIC:='1';

SIGNAL GRB: STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS (clk) --clk = 24MHZ hs = 30 Khz vs = 57hz

VARIABLE i : integer range 0 to 799:=0;

VARIABLE j : integer range 0 to 79:=0;

BEGIN

if reset = '1' then

GRB <= "000"; i:=96; j:=0; hs <= '1';

elsif clk'event and clk = '1' then

if i < 96 then

hs <= '0';

elsif i = 799 then

i:=0;

else

hs <= '1';

end if;

if j = 79 then

GRB(1) <= not GRB(1);

j:=0;

end if;

i:=i+1;

j:=j+1;

end if;

vga_hs_control <= hs;

END PROCESS ;

PROCESS (hs)

VARIABLE k : integer range 0 to 524:=0;

BEGIN

if reset = '1' then

k:=2; vs <= '1';

elsif hs'event and hs = '1' then

if k < 2 then

vs <= '0';

elsif k = 524 then

k:=0;

else

vs <= '1';

end if;

k:=k+1;

end if;

vga_vs_control <= vs;

END PROCESS ;

PROCESS (clk)

BEGIN

if clk'event and clk = '1' and vs = '1' and hs ='1' then

vga_green_dispaly <= GRB(2);

vga_read_dispaly <= GRB(1);

vga_blue_dispaly <= GRB(0);

end if;

END PROCESS ;

END a;

以上是源程序

下面是仿真图 RGB 三条输出全部没信号 不知道为什么

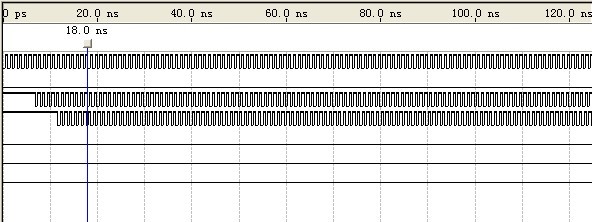

先解决一下行场同步的问题吧,都长的和时钟一样了

二楼说的对,行场同步有很严重的问题,你设计的分辨率是多少来的?

看来你的频率是1GHz,这是什么制式?用到这么高的频率?

if reset = '1' then

GRB <= "000"; i:=96; j:=0; hs <= '1';

elsif clk'event and clk = '1' then

if i = 799 then

i:=0;

else

i:=i+1;

end if;

if i < 96 then

hs <= '0';

else

hs <= '1';

end if;

if j = 79 then

GRB(1) <= not GRB(1);

j:=0;

else

j:=j+1;

end if;

改成这样子再试一下吧

FPGA语言?

呵呵没有看明白

没有看明白