关于SDRAM的简单问题,紧急求助!

郁闷了很久不知问题所在,用SIGNAL TAP II检查时序也还是不懂。

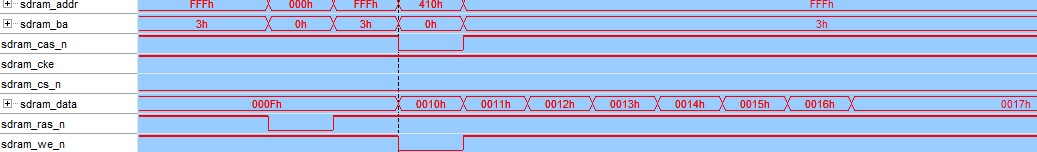

这是写的时序图 来自signalTap II ,大家可以看到FPGA确实在写了

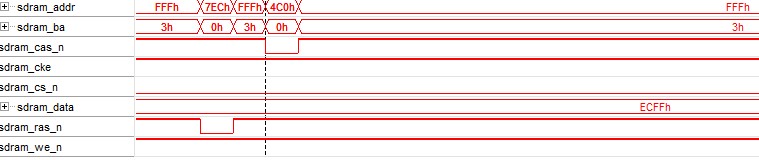

这是读的时序图,可是却读不出来东西,不明原因。

我目前猜想可能是没写进去,或者数据丢失,还望高手指点一二。

哎,怎么没人回呀,自己顶一个

读不出来可能的原因太多了,我们这里一个人搞DDR,读不出来的原因是。

DQ设置的是output 应该是bidir才对,嘿嘿,你不会也是这个弱智问题吧

没啊,数据线当然是要双向的啦。这个会不会是有细节的时序问题呢?是根本没写进去吗?

帮顶,一起学习

我不怎么会,希望有人能解决

有可能是sdram的时序配的不对,你能保证仿真时的模型和实际的sdram的颗粒在timing parameter上是一致的吗?

sdram出问题,很多都是自身的时序(相位)问题……所以首先还是把时序问题解决了,再进行下面的工作。

路过,来看看,学习了

有可能是时序上的问题吧

您说的时序我觉得是读写的命令之间所隔的时钟数目吧?可是跟相位关系大吗,还要做好时序约束?

与相位有一定的关系。前段时间调4块SDRAM时,出现的也是读写有问题,通过加DCM和相应的相位控制,基本上全解决了……当然你也最好细细的看一下你的SDRAM本身的硬件资料中读写时序是怎么控制的……

奥,我觉得时序的可能性很大,但是我新手所以对时序约束等内容了解比较浅,感觉如果进行时序分析的话会比较吃力。还有,想问下,预充电如果设置成自动的会有影响吗?我的工程中都是自动的,可是见资料上讲解的是非自动的。

学习下

建议你post-sim一下,保证解决。

百分之百是你code时序的问题,Modelsim免费版哪是仿真,那是“仿假”。

用其他的仿真器试试,结果肯定不对,但这就是实际的结果。

这就是为什么你把code down到fpga上出不来东西的结果

小编你需要把写读SDRAM分开来一步步的检查,照你描述的这样很难帮到你。

把问题细化成一个个的步骤,分而治之,就能找到问题的关键了。

读写SDRAM无非就是接口上的几个控制信号,没有你想像的那么困难。

祝你好运!