动态电路功耗不好,原因分析求助帖

时间:10-02

整理:3721RD

点击:

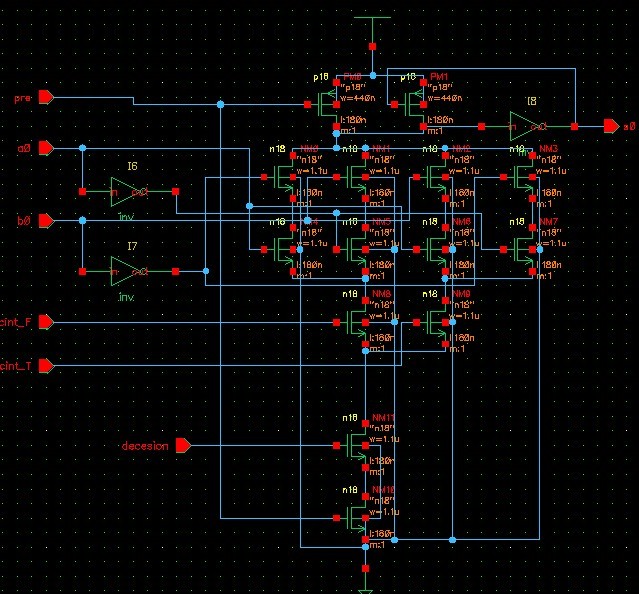

下面是参照国外文献做的一个比较器的一部分。

这是两位加法器的低位部分

[attach]356134[/attach]

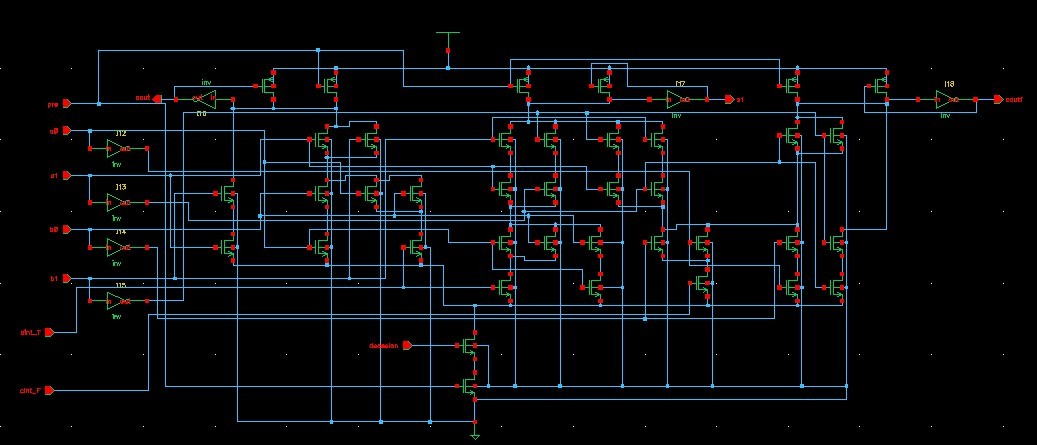

这是两位加法器的高位部分

据外国的文献说,这样的设计有较好的功耗效果。但实验结果表明比同步设计还高一倍。

现在想分析一下原因。可以大家可以多多指教

这是两位加法器的低位部分

[attach]356134[/attach]

这是两位加法器的高位部分

据外国的文献说,这样的设计有较好的功耗效果。但实验结果表明比同步设计还高一倍。

现在想分析一下原因。可以大家可以多多指教

希望大家可以给点意见,我想知道该如何着手分析

下预充管的位置错了,应该是控制整个的,而不是控制一条支路的;

看错了

沒看到電路.

dynamic complex gate.

Carry Chain上 Load相較於 complete CMOS, 沒有PMOS的 Cg, 所以速度較快.

缺點是抗noise能力差.

如果設計的好, 基本上dynamic circuit Power/Area/Speed 只會贏static 不會輸.

這點和一般書上可能不太一樣

不過現在除了幾家大家的(Intel/Apple...), 很少聽到有人用dynamic circuit.

要先认识电路的基本单元结构吧