FPGA复用的问题

时间:10-02

整理:3721RD

点击:

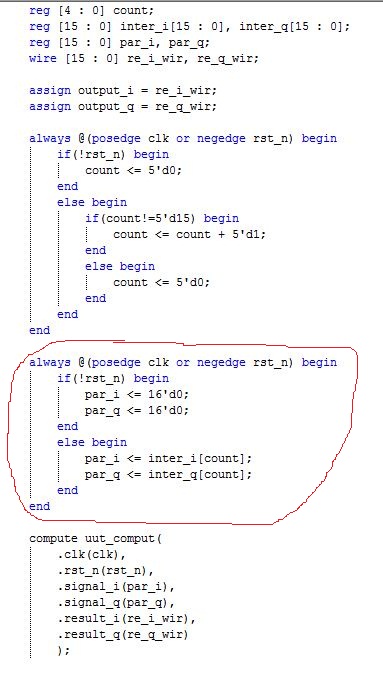

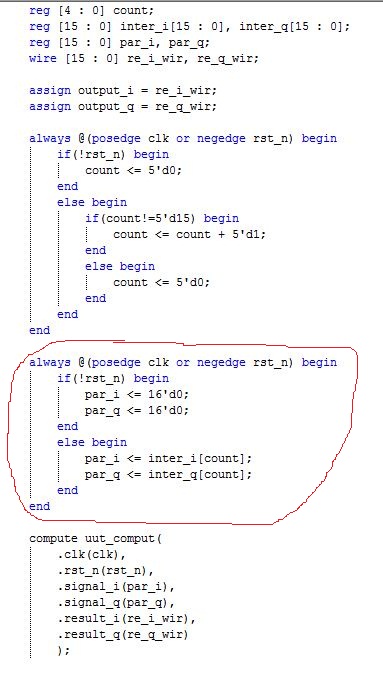

做一个小程序,希望对FPGA的资源消耗的越少越好,于是考虑到对关键的计算模块进行复用。

举例如下:

红框标记的为对计算模块的输入进行复用。

但是综合后发现复用这个过程本身消耗的资源已经远大于计算模块了,并且复用器消耗的资源随着选择的信号的个数和位宽正相关,当信号比较宽时,资源消耗非常大。

复用应该是一个很常见的问题,大家都是怎么解决的?

举例如下:

红框标记的为对计算模块的输入进行复用。

但是综合后发现复用这个过程本身消耗的资源已经远大于计算模块了,并且复用器消耗的资源随着选择的信号的个数和位宽正相关,当信号比较宽时,资源消耗非常大。

复用应该是一个很常见的问题,大家都是怎么解决的?

这部分逻辑是不可避免的

有没有其他复用办法?

比如说把待复用的信号写到RAM中,然后根据地址线去选择,这样用的是片上RAM自带的逻辑选择。

没看懂。

如果能这样当然是可以啦

之前的思路就是一般认为的面积换性能的一个典型吧。

没上下文的,我也看不明白这段红框内的用来干嘛

thanks

在综合选项中设置了resource sharing后,并且综合目标设为时序或面积优先后,综合工具会对简单的复用自动进行处理的,

对于简单的代码比较复用资源和时序表现等不明显,出现相反的情况也正常,如果是大规模的设计,采用类似的设计后,效果应很明显的,那时综合工具就不够智能了,还是要靠代码设计