寄存器输出出现数据不稳定! 望大虾指点

时间:10-02

整理:3721RD

点击:

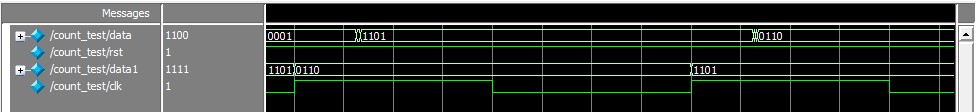

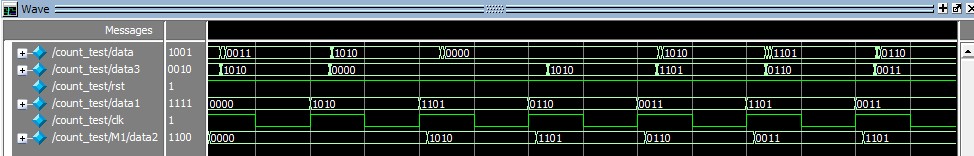

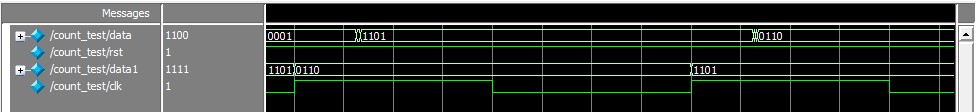

我将4位的输入 在时钟上升沿赋给输出寄存器,结果输出寄存器在数据稳定前 出现不该有的值!

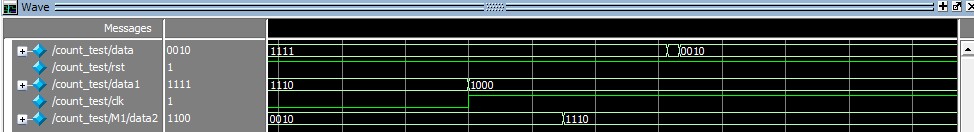

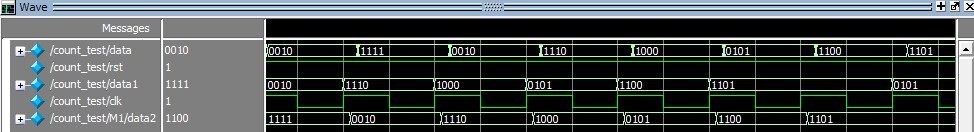

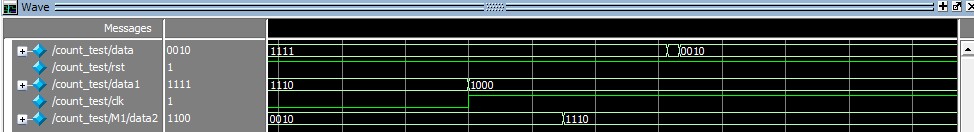

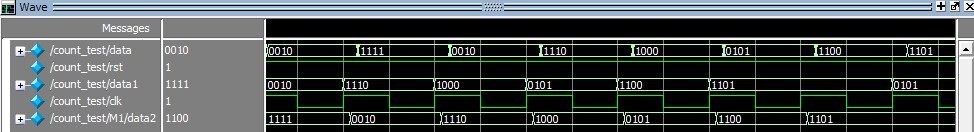

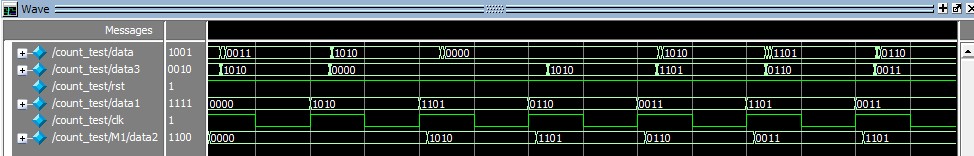

我又在输出和输入之间加入了一级中间寄存器,输入给中间寄存器,中间寄存器在给输出,结果中间寄存器的数据稳定变化,输出端不稳定。在加中间寄存器后,结果类似:输出端不稳,中间寄存器稳定。我又把中间寄存器也作为输出,结果输出端和作为输出的中间寄存器输出都不稳定 望大虾指点!代码如下:

直接复制的代码:

module count(data,data1,clk,rst);

output [3:0] data;

input clk;

input rst;

reg [3:0] data;

input [3:0] data1;

always@(posedge clk )

if(rst==0)

data<=1110;

else

data<=data1;

endmodule // count

中间加了一个寄存器data2后的代码:

module count(data,data1,clk,rst);

output [3:0] data;

input clk;

input rst;

reg [3:0] data;

input [3:0] data1;

reg [3:0] data2;

always@(posedge clk )

if(rst==0)

data2<=0;

else

data2<=data1;

always@(posedge clk)

data<=data2;

endmodule // count

加了中间寄存器data2 data3后的代码同时将data3作为输出的代码:

module count(data,data1,data3,clk,rst);

output [3:0] data;

input clk;

input rst;

reg [3:0] data;

input [3:0] data1;

reg [3:0] data2;

output reg [3:0] data3;

always@(posedge clk )

if(rst==0)

data2<=1110;

else

data2<=data1;

always@(posedge clk)

data3<=data2;

always@(posedge clk)

data<=data3;

endmodule // count

testbench

`timescale 1ns/1ns

module count_test();

wire [3:0] data;

wire [3:0] data3;

reg rst;

reg [3:0] data1;

reg clk;

count M1(.data(data),.data3(data3),.data1(data1),.clk(clk),.rst(rst));

initial #3000 $finish;

initial

begin

clk=0;

forever #20 clk=~clk;

end

initial

begin

rst=1;

#10 rst=0;

#35 rst=1;

end

always@(posedge clk)

data1<={$random}%16;

endmodule // count_test

我又在输出和输入之间加入了一级中间寄存器,输入给中间寄存器,中间寄存器在给输出,结果中间寄存器的数据稳定变化,输出端不稳定。在加中间寄存器后,结果类似:输出端不稳,中间寄存器稳定。我又把中间寄存器也作为输出,结果输出端和作为输出的中间寄存器输出都不稳定 望大虾指点!代码如下:

直接复制的代码:

module count(data,data1,clk,rst);

output [3:0] data;

input clk;

input rst;

reg [3:0] data;

input [3:0] data1;

always@(posedge clk )

if(rst==0)

data<=1110;

else

data<=data1;

endmodule // count

中间加了一个寄存器data2后的代码:

module count(data,data1,clk,rst);

output [3:0] data;

input clk;

input rst;

reg [3:0] data;

input [3:0] data1;

reg [3:0] data2;

always@(posedge clk )

if(rst==0)

data2<=0;

else

data2<=data1;

always@(posedge clk)

data<=data2;

endmodule // count

加了中间寄存器data2 data3后的代码同时将data3作为输出的代码:

module count(data,data1,data3,clk,rst);

output [3:0] data;

input clk;

input rst;

reg [3:0] data;

input [3:0] data1;

reg [3:0] data2;

output reg [3:0] data3;

always@(posedge clk )

if(rst==0)

data2<=1110;

else

data2<=data1;

always@(posedge clk)

data3<=data2;

always@(posedge clk)

data<=data3;

endmodule // count

testbench

`timescale 1ns/1ns

module count_test();

wire [3:0] data;

wire [3:0] data3;

reg rst;

reg [3:0] data1;

reg clk;

count M1(.data(data),.data3(data3),.data1(data1),.clk(clk),.rst(rst));

initial #3000 $finish;

initial

begin

clk=0;

forever #20 clk=~clk;

end

initial

begin

rst=1;

#10 rst=0;

#35 rst=1;

end

always@(posedge clk)

data1<={$random}%16;

endmodule // count_test

你的data1实在时钟上升边沿变化的,同时也在采样,也就是边沿采样边沿的问题,QQ群:127971002;欢迎一起交流

我感觉,最后一步换成过程连续赋值语句assign data=data1试试,是不是能好点。

你這個是在做后仿呢?如果是後方,這個正常,如果是前仿,肯定是工具的問題,代碼應該沒有問題。

做后仿的话,由于不同的单元有不同的时序信息,稳定前的抖动是不可避免的。

有些仿真工具就是这样 的!

你可以用 a <= #1 b;

来解决这个问题!

我也想知道啊

你这个是做后仿。延迟参数是你自己加的吗?这样的代码书写没有问题,实际情况不会出现这种现象。