询问一个输出延时的问题,VERILOG的

三个脉冲的周期都为20ms,占空比1:2。

其中firen2对于firen延时30°,firen3对于firen2 延时30°。

如何用verilog hdl实现?

不甚感激 ,尤其是想知道用计数器如何实现延时。有源代码吗?

谢谢··

急···

脉冲的周期?脉冲只有正负脉冲和脉冲宽度的这样的定义。

你的应该是周期信号,还有周期和占空比以及延时相位一说。如果是脉冲就只有绝对延时了。

若只是用来描述,产生测试激励,很简单。

1ns 分频出 20ms period 的波形文件很简单。

占空比也不难。难点在于你要的30度,如果激励,算好了时间 # (20 *(30/360)) 就可以了。

若是设计电路,前端描述,综合,延时会被忽略就没用了。

这个情况,你或许可以试试看set_min_delay 加在两个端口上。

DC会推断出好多delay cell,至于最后出来是不是精确的30度,难说。

最好的做法当然是用现成的PLL DLL了。

通过记主时钟的个数就可以延时的计量,比如你这里1M的时钟,一个时钟周期就可以产生1us的延时,对于20ms周期的30度就是20ms/12=1667us,所以你要通过计数延时1667个时钟周期。

占空比 20ms的都知道怎么写 就是不知道如何延时30° 直接用#这样的话 那应该使用于测试中 综合上好像不能用

我想知道如何将这个30°延时的计数器运用到延时中?是否可以用寄存器?

可以用,就是用寄存器计数来标定30度的,即一个周期的1/12,20000*1/12 = 1667啊!

module fen(

clkin,

reset,

firen1,

firen2,

firen3,

counter1,

counter2,

counter3

);

input clkin;

input reset;

output firen1,firen2,firen3;

output [14:0] counter1,counter2,counter3;

reg firen1,firen2,firen3;

reg [14:0] counter1,counter2,counter3;

//20ms:20000, P:6667,N:13333 30du:1667 counter:23334

always @(posedge clkin)

begin

if(reset)

begin

counter1 <= 15'D0;

counter2 <= 15'D0;

counter3 <= 15'D0;

end

else

begin

if(counter1 >= 15'D19999)

counter1 <= 0;

else

counter1 <= counter1 + 15'D1;

if(counter1 == 15'D1666)

counter2 <= 0;

else

counter2 <= counter2 + 15'D1;

if(counter2 == 15'D1666)

counter3 <= 0;

else

counter3 <= counter3 + 15'D1;

end

end

always @(negedge clkin)

begin

if(counter1 < 15'D6667)

firen1 <= 1;

else

firen1 <= 0;

if(counter2 < 15'D6667)

firen2 <= 1;

else

firen2 <= 0;

if(counter3 < 15'D6667)

firen3 <= 1;

else

firen3 <= 0;

end

endmodule

非常感谢 我好好看下

学习一下

感谢分享

不用客气,呵呵。

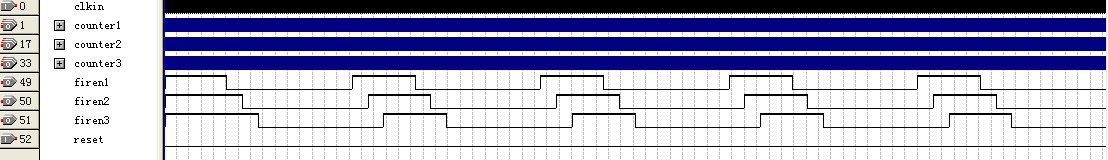

见图,firen2 firen3 `波形 第一个周期的时间大于后面的周期 ··后面的周期都为20ms 占空比也都为1:2

但是第一周期就比较大 ··

根据您的代码,counter2 在 counter1计数小于1666的时候也在计数 这时候firen输出也为1

counter3相对于counter2也类似

能够让脉冲第一个周期的时间也一样?

module firen2(clk,rst,firen,firen1);

input clk;

input rst;

output firen;

output firen1;

reg [14:0]count;

reg firen;

reg firen1;

always@(posedge clk or posedge rst )

if (rst)

count<=15'D0;

else if(count<20000)

count<=count+15'D1;

else

count<=15'D0;

always@(posedge clk or posedge rst)

if (rst)

firen<=0;

else if(count<6666)

firen<=1;

else

firen<=0;

always@(posedge clk or posedge rst)

if (rst)

firen1<=0;

else if((count>1666)&&(count<8333))

firen1<=1;

else

firen1<=0;

endmodule

在时间的取值上好像不是很准确 这是用纯粹计数器计算的··那样第一个周期也会延时

LQ4080 这样是否可以?

只要你在Reset之后,不要都复位,counter3 <= 15'D0;counter2 <= 15'D1667;counter3 <= 15'D3334就行了,第一个周期也能满足。

学习了