对于上升沿和下降沿的疑惑

时间:10-02

整理:3721RD

点击:

一个verilog的教程里说,z->0是下降沿,z->1是上升沿

可是,D触发器的CP信号,我怎么感觉输入z和输入1是一个效果呢?

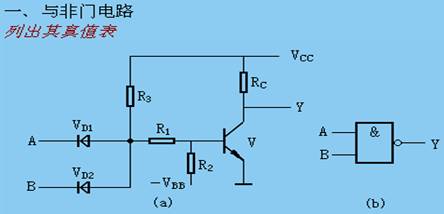

D触发器由几个与非门组成,,而与非门的输入端又是二极管

二极管输入端为高电平和高阻态的效果不是一样的么?

想了很久没想明白

在Google里查了n久没查到什么东西,,,只好来问了

可是,D触发器的CP信号,我怎么感觉输入z和输入1是一个效果呢?

D触发器由几个与非门组成,,而与非门的输入端又是二极管

二极管输入端为高电平和高阻态的效果不是一样的么?

想了很久没想明白

在Google里查了n久没查到什么东西,,,只好来问了

我的理解是,书上说的是逻辑层面的边沿变化,就是针对变量的九值逻辑,而下面说的D触发器则是电路层面的,就是说具体实现上的高阻态,可能不一定是一个东西。

于上升沿和下降沿的

我觉得你说的是仿真的时候的变化,跟硬件电路是不相关。

tmpfileinfo = this->list.at(this->m_bookList->getoffset()+0);

正解,z->0 和 z->1 只是纯语法或者说纯仿真的问题,仿真时的定义

实际硬件电路,如果是CMOS输入的话,不允许输入端出现Z状态;

如果是TTL电路,如图的话,Z和1是一样的,没有边沿的改变