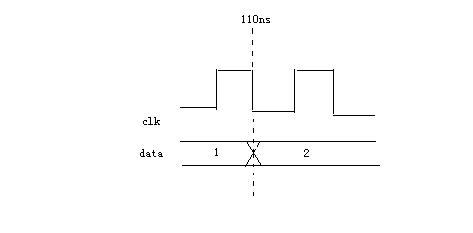

对于这样的时序图,仿真器怎么采样值是什么?

时间:10-02

整理:3721RD

点击:

如下图,在110ns时,仿真器采到的data的值是1还是2?

附件这次才上传成功,不好意思,大家给指点一下,主要从仿真器的仿真原理方面解释,多谢!

是1,这与仿真器的原理无关,是时序电路特点决定的。2是updata出来的值

我使用altera器件,用到了仿真库altera_mf.v里的altddio_in模块,这个模块的作用是把输入数据用给定时钟进行上下沿采样,输出高bits和低bits。

我发现,在modelsim 6.0下,对于上图的110ns处采样值为1,在questasim 6.5下,采样到的为2。

还没有完,我在工程里加入另一个测试模块,像功能代码里一样来使用altddio_in模块,在modelsim 6.0下,功能代码里采样1,我的例子采样2。在questasim 6.5下,结果不变都是2。

这该怎么解释呢?

你的电路是否满足建立时间和保持时间呢?

在采样时钟沿处,数据要稳定!

如果你要研究模拟器在这种情况下如何工作,那就因仿真器而异了,我也不知道了。

给data加1ns的dly吧,仿真好看点,下降沿采样肯定是1

加上dly肯定没问题,问题是在modelsim6.0下仿真OK,同步到questasim6.5就仿真不过了,一直追到这里来的。

楼上的两位说的都没错,在保持时间不满足时的条件下,仿真器的行为是不是不确定的?

加上dly肯定没问题,问题是在modelsim6.0下仿真OK,同步到questasim6.5就仿真不过了,一直追到这里来的。

楼上的两位说的都没错,在保持时间不满足时的条件下,仿真器的行为是不是不确定的?

``再顶