VHDL unsigned signal有语法错误,麻烦看看

然后是个process,每clk 加1

再引用

case cnt is;

when 1 =>

....

when 2 =>

.....

modelsim报错:Integer literal 1 is not of type ieee.numeric_std.unsigned

请指出问题所在

可能是你的库没有加全。下面是我写的一段程序,经测试没有问题。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity test is

port(

clk : in std_logic;

rst : in std_logic;

p : out std_logic

);

end entity;

architecture test_arch of test is

signal cnt: unsigned(2 downto 0);

begin

p<='1' when cnt=2 else '0';

process(clk)

begin

if rising_edge(clk) then

if rst='1' then

cnt <= (others=>'0');

else

cnt <= cnt+1;

end if;

end if;

end process;

end test_arch;

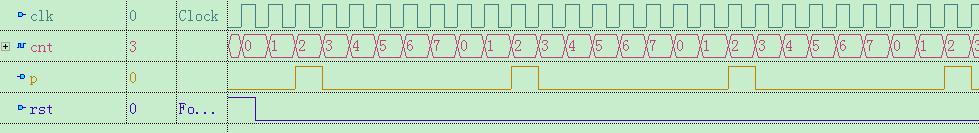

这是仿真结果,。

仿真软件Active-HDL 8.2,,,,,,,,,

另外,使用这两个库也是可以的

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

事实上,std_logic_1164和numeric_std是标准库。

when "0000001" =>

请用这样的格式。VHDL是不能偷懒的

支持6楼

VHDL还是可以偷懒的,是你的库没加对。

嗯,如6楼所言,

如果是if语句中,可以用unsigned singal = num,但是在case语句是,还是得用二进制,这几天的发现。