CPLD管脚约束的问题

时间:10-02

整理:3721RD

点击:

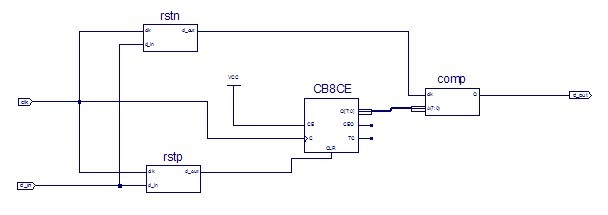

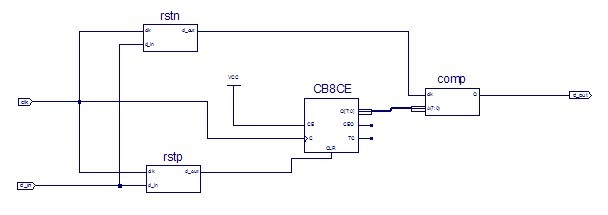

最近做一个设计,用的是CPLD XCR3064XL,工具为ISE9.0,我的顶层接口是clk,d_in,d_out三个管脚,如下图:

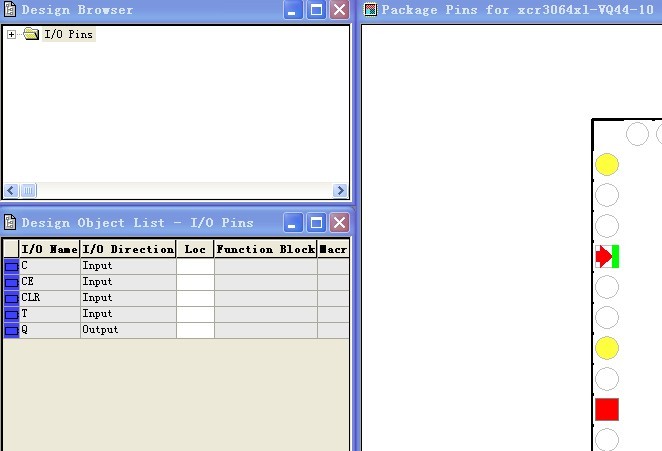

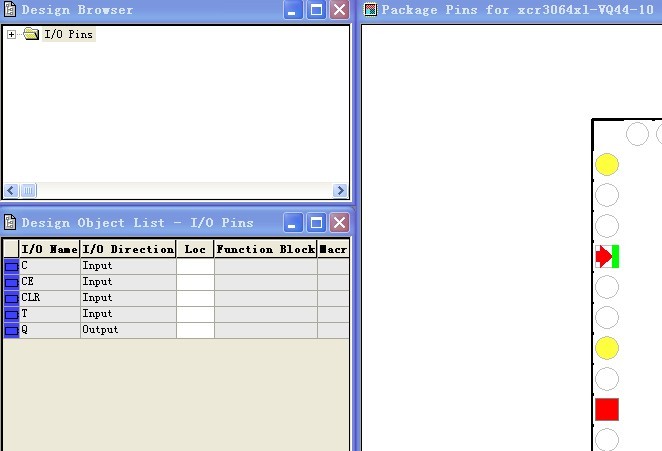

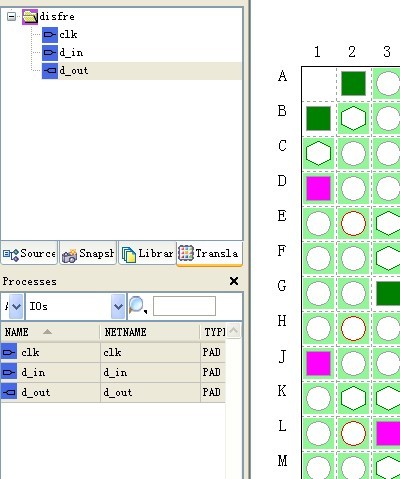

可是当我分配管脚时却出现了另外的接口信号,如下图

不太明白这是为什么,请高手指教下,谢谢 !

可是当我分配管脚时却出现了另外的接口信号,如下图

不太明白这是为什么,请高手指教下,谢谢 !

最后一个图是芯片换成FPGA V4后就可以了,但是CPLD为什么不行呢》?

感觉这个好像是CB8CE的管脚,具体也不是很清楚了。

观察“View Technology Schematic”是正确的,显示的就是我设置的端口,手工写了“Edit Constraints”,如下:

NET "clk" LOC = P2;

NET "d_in" LOC = P4;

NET "d_out" LOC = P5;

再次点击“Assign Package Pins”,,显示如下错误:

Compiling verilog file "E:\Data\FPGA\exercise\syswith\disfre.v"

ERROR:designEntry - Could not apply constraint:

NET "clk" LOC = P2;

ERROR:designEntry - Could not apply constraint: NET "d_in" LOC = P4;

ERROR:designEntry - Could not apply constraint: NET "d_out" LOC = P5;

伤脑筋呀,这不会是BUG吧

这是ISE的一个BUG,只有CPLD会出现,FPGA不存在,当自建模型和库模型在设计中同时出现时,系统优先综合库模型,也就会出现本例中像计数器一样的端口。解决办法是修改以顶层文件命名的.vf文件,调换库综合后果的代码和自建模型综合后的代码的位置,就OK了。