{S-O-S}FPGA控制ADC0809?

时间:10-02

整理:3721RD

点击:

利用FPGA控制ADC0809完成采样,有问题结果,下面是程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adc is

port ( d : in std_logic_vector(7 downto 0) ; ----ADc0809的结果输入FPGA

fuwei : in std_logic; ----复位信号

adclk : in std_logic; ---时钟

ale : out std_logic; ---地址锁存

start : out std_logic; ---开始信号

eoc : in std_logic; ---转换信号

oe : out std_logic; --oe是输出使能信号,

lock0 : out std_logic; ---lock和lock0是oe的copy,用于下一级的

adda : out std_logic; --地址信号

q : out std_logic_vector(7 downto 0) );----ADC转换结果

end adc;

architecture str of adc is

signal lock:std_logic;

signal current_state:std_logic_vector(4 downto 0);

constant st0:std_logic_vector(4 downto 0):="00000";

constant st1:std_logic_vector(4 downto 0):="01100";

constant st2:std_logic_vector(4 downto 0):="10000";

constant st3:std_logic_vector(4 downto 0):="00011";

begin

adda<='0'; ----在调试是应使用 way0(addb,addc已接地)

ale<=current_state(3);start<=current_state(2); --ale是地址锁存信号

oe<=current_state(1);lock <=current_state(0);lock0<=current_state(0);

------state控制进程

com: process(eoc,adclk,fuwei)

BEGIN

if fuwei='1' then current_state<=st0; ----复位状态

elsif( adclk'event and adclk='1') then

case current_state is ---判断current_state

when st0 => current_state<=st1;

when st1 => current_state<=st2;

when st2 => if eoc='1' then

current_state<=st3;

else current_state<=st2;

end if;

when st3 => current_state<=st0;

when others=>current_state<=st0;

end case;

end if;

end process com;

latch:process(lock) ----输出转换结果

begin

if lock'event and lock='1' then

q<=d;

end if;

end process latch;

end str;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adc is

port ( d : in std_logic_vector(7 downto 0) ; ----ADc0809的结果输入FPGA

fuwei : in std_logic; ----复位信号

adclk : in std_logic; ---时钟

ale : out std_logic; ---地址锁存

start : out std_logic; ---开始信号

eoc : in std_logic; ---转换信号

oe : out std_logic; --oe是输出使能信号,

lock0 : out std_logic; ---lock和lock0是oe的copy,用于下一级的

adda : out std_logic; --地址信号

q : out std_logic_vector(7 downto 0) );----ADC转换结果

end adc;

architecture str of adc is

signal lock:std_logic;

signal current_state:std_logic_vector(4 downto 0);

constant st0:std_logic_vector(4 downto 0):="00000";

constant st1:std_logic_vector(4 downto 0):="01100";

constant st2:std_logic_vector(4 downto 0):="10000";

constant st3:std_logic_vector(4 downto 0):="00011";

begin

adda<='0'; ----在调试是应使用 way0(addb,addc已接地)

ale<=current_state(3);start<=current_state(2); --ale是地址锁存信号

oe<=current_state(1);lock <=current_state(0);lock0<=current_state(0);

------state控制进程

com: process(eoc,adclk,fuwei)

BEGIN

if fuwei='1' then current_state<=st0; ----复位状态

elsif( adclk'event and adclk='1') then

case current_state is ---判断current_state

when st0 => current_state<=st1;

when st1 => current_state<=st2;

when st2 => if eoc='1' then

current_state<=st3;

else current_state<=st2;

end if;

when st3 => current_state<=st0;

when others=>current_state<=st0;

end case;

end if;

end process com;

latch:process(lock) ----输出转换结果

begin

if lock'event and lock='1' then

q<=d;

end if;

end process latch;

end str;

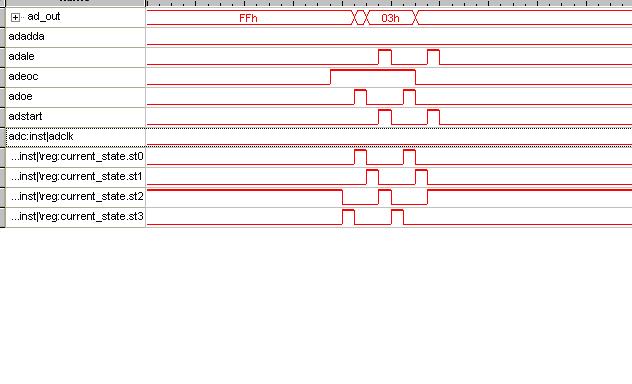

上一帖的图片

这是用SignaltapII仿真得到的图片,错误点就是四个状态位执行了两次,ale,start,oe也有两个高脉冲,找了好久,不知道错误原因啊.大家帮忙侃侃!

好!