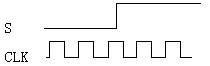

如何检测信号的上升沿?

用clk去检测s信号?不明白你的意思。

如果只是要检测s信号,可以用一个寄存器,对当前s信号与前一s信号进行异或,并判断当前s信号的值即可。

编个VHDL程序就可以了呀

(clk'event and clk='1')

用移位寄存器

用移位寄存器,每个时钟采S的值,当移位寄存器的Q端为0而D端为1时,即为上升沿.为了消除亚稳态,建议再加两个移位积存器来消除亚稳态.

没看出有什么意义啊

......

{t2,t1} <= #1 {t1,d};

pe = (0==t2) & (1==t1);

1)线路测试用示波器就可以了;

2)JTAG测试,建议用更高的clk,以提高采样精度

用识别器边沿触发模式

简单的检沿电路

module(clk,reset,a,b);

input clk;

input reset;

input a;

output b;

reg a_r;

always (posedge clk or negedge reset)

begin

if (!reset)

a_r<=1'b0;

else

a_r<=a;

end

assign b=a_r && a;

修改一下

module(clk,reset,a,b);

input clk;

input reset;

input a;

output b;

reg a_r;

always (posedge clk or negedge reset)

begin

if (!reset)

a_r<=1'b0;

else

a_r<=a;

end

assign b=!a_r && a;

//上升沿检测模块,要求信号保持时间在一个clock周期以上

module rising_edge_check(clock, signal, rising_flag);

input clock;

input signal;//input signal

output rising_flag;//rising edge flag

reg [2:0] temp=3'b000;

always @(posedge clock)

temp<={temp[1:0],signal};

assign rising_flag=(temp[1:0]==2'b01)?1'b1:1'b0;

endmodule

//testbench

module test_rising_edge_check_v;

// Inputs

reg clock;

reg signal;

// Outputs

wire rising_flag;

// Instantiate the Unit Under Test (UUT)

rising_edge_check uut (

.clock(clock),

.signal(signal),

.rising_flag(rising_flag)

);

initial begin

// Initialize Inputs

clock = 0;

signal = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

signal=1;

#500;

signal=0;

#500;

signal=1;

#200;

signal=0;

#100;

signal=1;

#300;

signal=0;

end

always #100 clock=~clock ;

endmodule

temp<={temp[1:0],signal};

请问这条语句是什么意思

还是有收获的

还是有收获的