关于两端口ROM的问题

时间:10-02

整理:3721RD

点击:

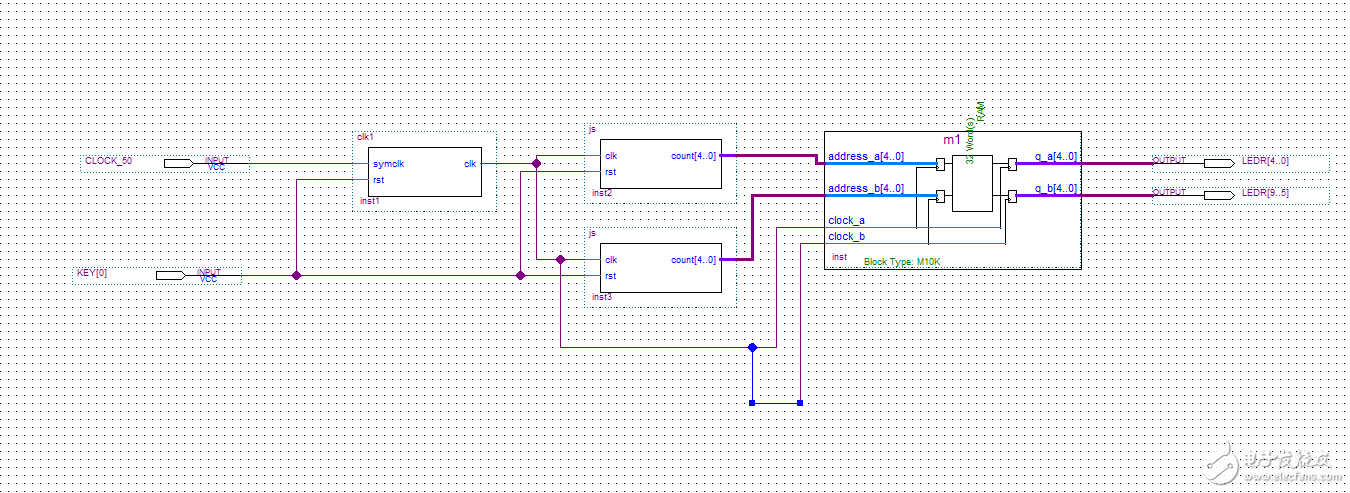

最近我写的一个程序要用比较大的table,所有要用一定的记忆体去存储。由于我的table在操作过程中是不变的,所以我选用rom。为了提高工作频率,我使用了并行处理。比如现在我的table要占1Mb的rom,当我要并行处理41个模块时,那么就使用了41Mb的记忆体。所以我想如果能有一个多输入多输出,便能共享1个1Mb的记忆体。所以我自己写了个41输入41输出的rom,然而系统给的综合报告和之前用的内存大小相差无几。 但是我又看到系统的IP核有一个2输入2输出的rom,我试着例化,即使用20个2输入2输出的rom,1个1输入1输出的rom,和41个1输入1输出的rom的相比,能存占用真的减少了一半。所以我的问题是,这个IP核的2输入2输出的rom的设计原理是什么呢,为什么就能做到共享一个记忆体呢?我问我老师,他认为一个时钟只能有一个进一个出望各位不吝赐教,然而这里我只给了一个时钟,他同时有两个输入和输出,而且资源利用提高了,工作频率也没降低,感谢!

此问答贴被选为3月1日的每日一答贴,活动详情见:http://bbs.elecfans.com/jishu_1111064_1_1.html 希望大家可以踊跃帮助坛友解决问题,谢谢。

多口rom ram,,其实就是共享

但是我自己写的多口rom ram不能实现共享 我的问题是Ip core 的rom是怎样做的, 或者怎样的原理, 谢谢!

感激不尽!

希望小编能得到满意的答案~

双口ram虽然有两个写口,但使用时不可以同一时间对同一地址进行写操作,否则会出现不定的值,这点应该仿真就可以看出来,读的时候无所谓,你两个口都读一个地址,他的值也不变,你也可以assign给100个端口。

我经过综合后都下到板子上测试了,结果是正确的。

学习了,谢谢分享

!

应该是一个芯片只是写入,一个芯片进行读取。

如果你是想将“同一个rom”中的内容并行赋值给多个模块使用,那么只需要一个rom ,一套读操作,将输出的数据同时赋值给不同的模块即可,即多个assign ;

如果不同的模块所使用的rom 中内容不一样,那么一个多输入多输出的rom 和多个单输入单输出的rom 是没有区别的。

你可以调用IP核,看看里面的代码会怎么实现的

您好!我也遇到了同样问题,我不知道ROM:2-PORT模块怎么用?请您教我一下,或者给我发个工程,我学习一下ROM:2-PORT模块使用,我的邮箱:1072271062@qq.com