开箱简介及基本资源上手

时间:10-02

整理:3721RD

点击:

好久没见过FPGA了,感谢锆石科技和电子发烧友。等了一个星期的某宝15块的usb blaster很好用。

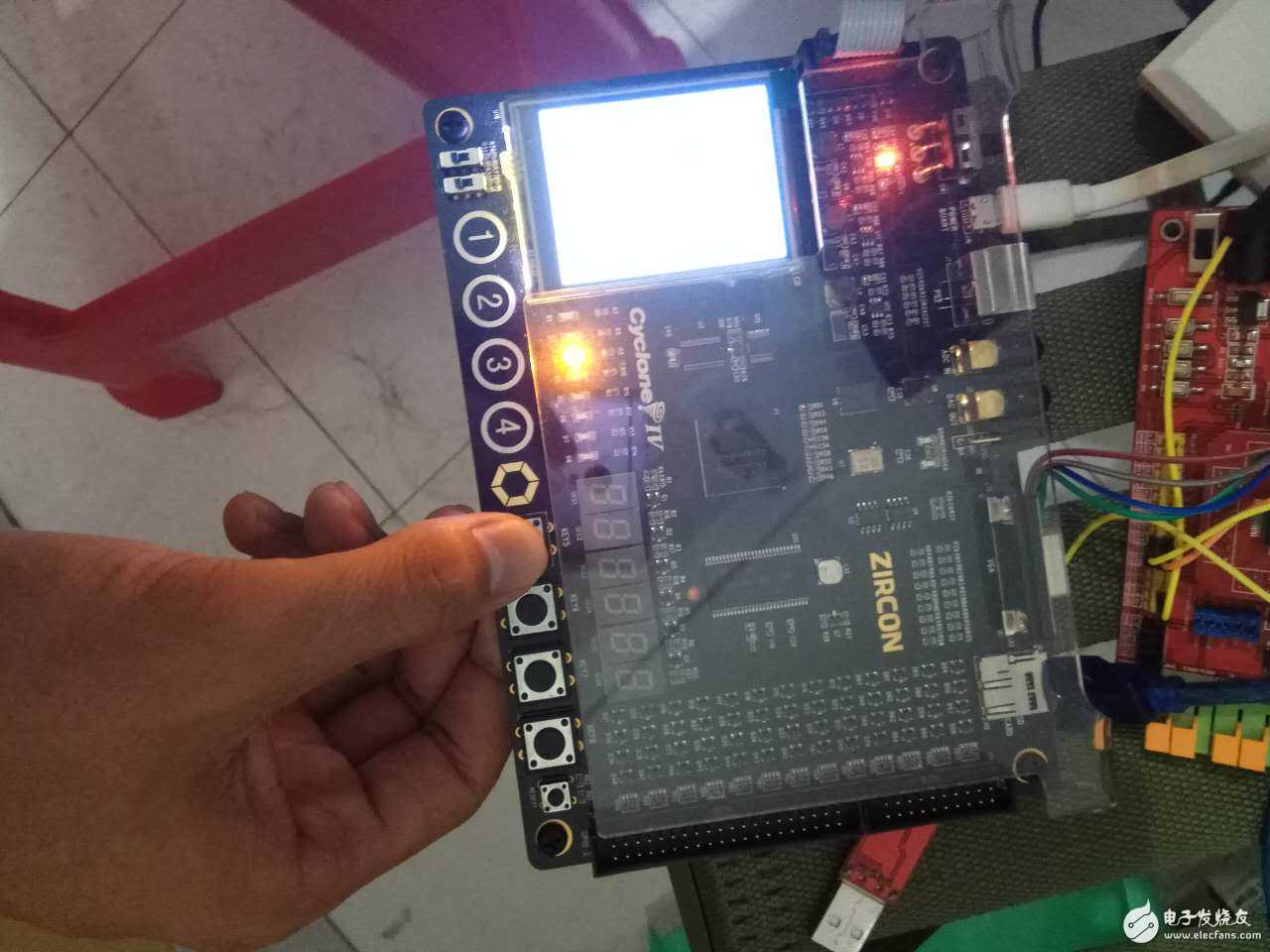

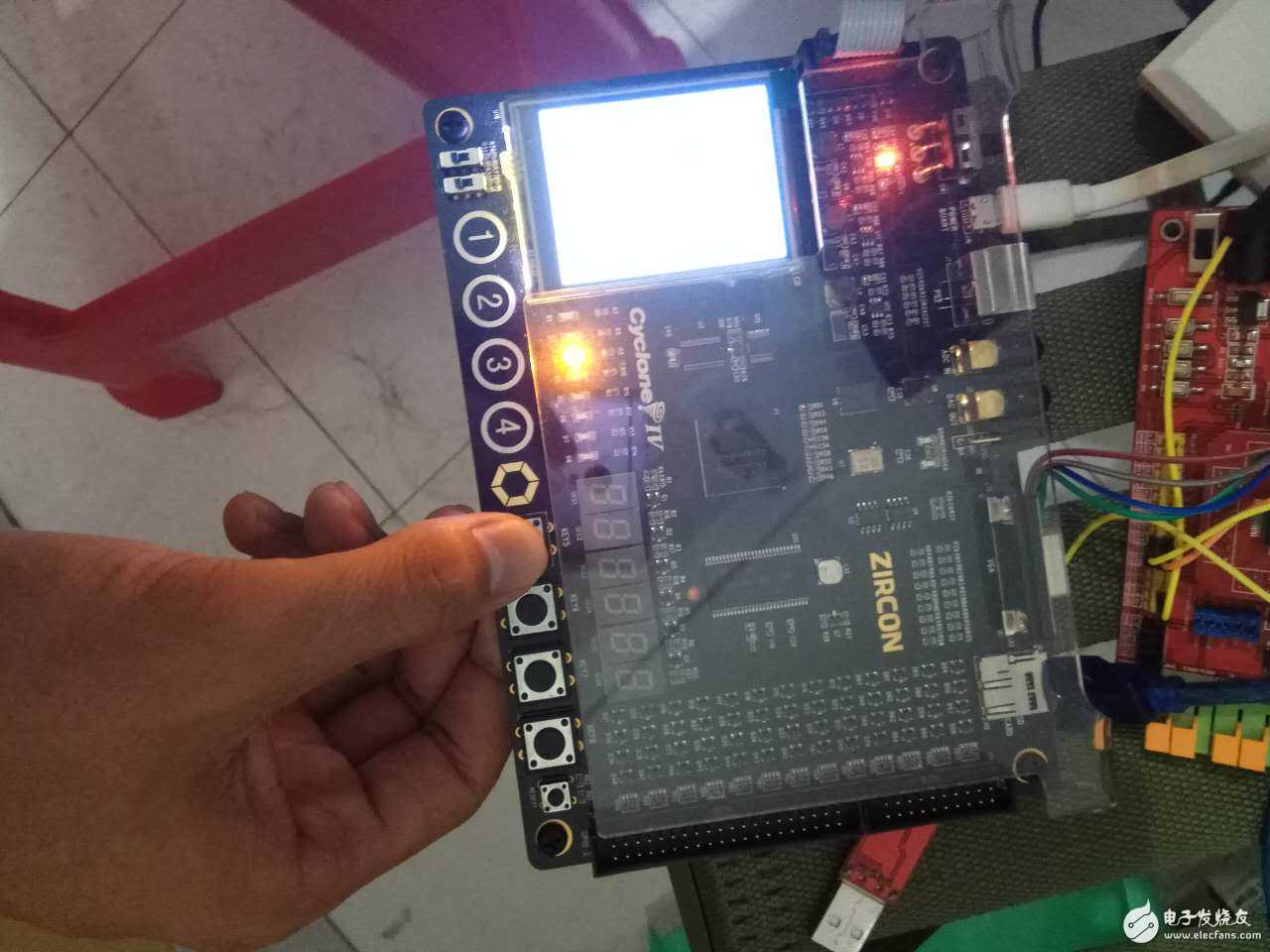

外观以及我的下载器就长这样了。

首先得看它们的管脚分配,然后这样简单的测试一下:

//水一发再说

module lab1(input gnd1,

input vdd1,//只是单纯的验证管脚功能,可在程序中直接用1/0代替

input reset,//按下去将产生下降沿

input clk,//50MHz,50M分频需要25位的D触发器来分频

output led1,

output led2,

output led3,

output led4);

reg test_ck;

reg [24:0] count;

always@(posedge clk or negedge reset)begin

if(~reset)begin count<=0;test_ck<=0;end

else begin count<=count+1;

if(count==0)test_ck<=~test_ck;

end //此句将产生latch?

end

assign led1=1'b0;

assign led2=1'b1;

assign led3=vdd1&test_ck;

assign led4=vdd1|gnd1;

endmodule

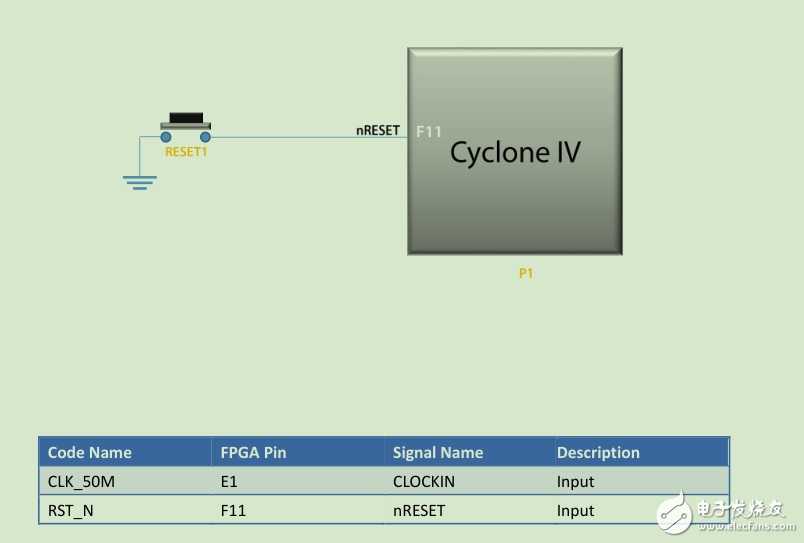

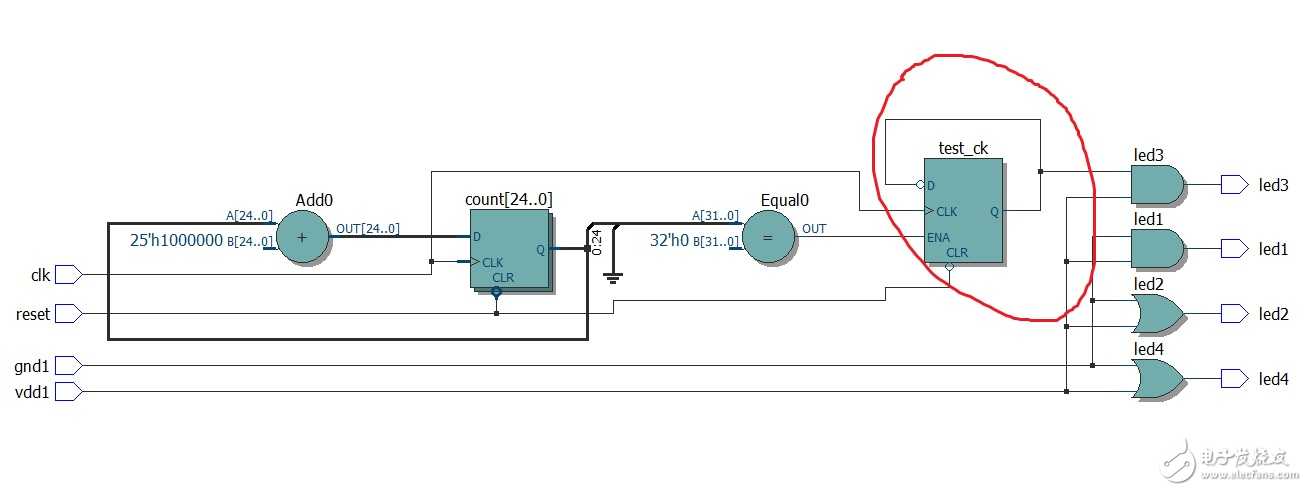

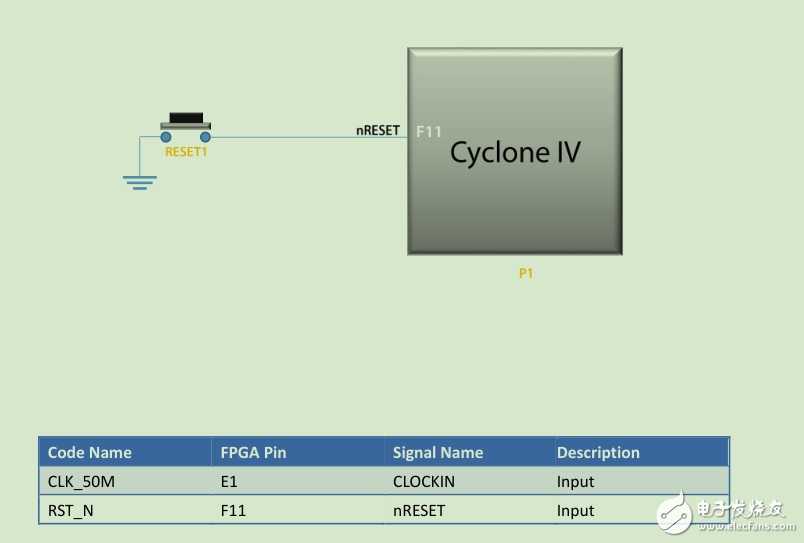

这个程序主要用到了50MHz的时钟源E1,复位信号F11,以及几个按键和LED。下载到板子上之后,按一下Reset按键,可以看到的现象就是一个LED一直亮着,另外一个LED,如果按下key6(该引脚接VDD),那么LED3就跟随者50M分频之后的1Hz时钟在闪烁,照片如下。

下载之后,断电重启则丢失全部的数据,重新回到默认的按键响音符的程序中。值得一提的是,Reset按下之后并不是对应着“PC指向Reset handler”这类的操作,而是一个简单的下降沿电平。

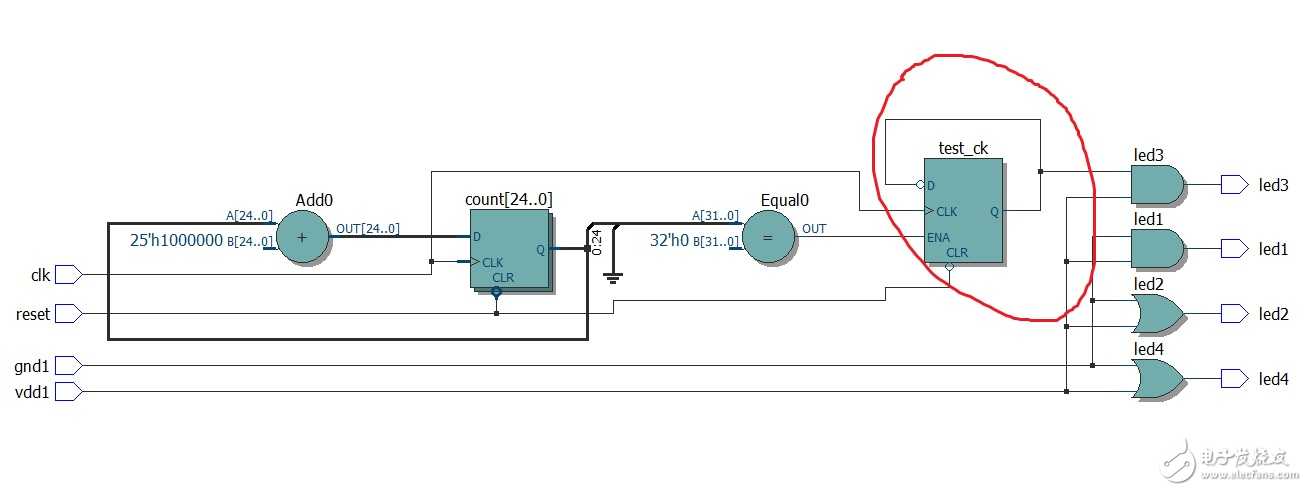

在quartus里,compilation代表综合、汇编的意思。执行这个操作后,verilog被综合为网表;分配管脚之后再次综合即可下载到FPGA上。(单次)上述代码综合的结果如下:

可以看到,虽然if没有全覆盖,但是并没有生成latch。细思之,这个逻辑的实现方法是对的。

如果实现一句话的唯一方法是锁存器,那么才会综合出锁存器吧。最后附一张管脚图:

外观以及我的下载器就长这样了。

首先得看它们的管脚分配,然后这样简单的测试一下:

//水一发再说

module lab1(input gnd1,

input vdd1,//只是单纯的验证管脚功能,可在程序中直接用1/0代替

input reset,//按下去将产生下降沿

input clk,//50MHz,50M分频需要25位的D触发器来分频

output led1,

output led2,

output led3,

output led4);

reg test_ck;

reg [24:0] count;

always@(posedge clk or negedge reset)begin

if(~reset)begin count<=0;test_ck<=0;end

else begin count<=count+1;

if(count==0)test_ck<=~test_ck;

end //此句将产生latch?

end

assign led1=1'b0;

assign led2=1'b1;

assign led3=vdd1&test_ck;

assign led4=vdd1|gnd1;

endmodule

这个程序主要用到了50MHz的时钟源E1,复位信号F11,以及几个按键和LED。下载到板子上之后,按一下Reset按键,可以看到的现象就是一个LED一直亮着,另外一个LED,如果按下key6(该引脚接VDD),那么LED3就跟随者50M分频之后的1Hz时钟在闪烁,照片如下。

下载之后,断电重启则丢失全部的数据,重新回到默认的按键响音符的程序中。值得一提的是,Reset按下之后并不是对应着“PC指向Reset handler”这类的操作,而是一个简单的下降沿电平。

在quartus里,compilation代表综合、汇编的意思。执行这个操作后,verilog被综合为网表;分配管脚之后再次综合即可下载到FPGA上。(单次)上述代码综合的结果如下:

可以看到,虽然if没有全覆盖,但是并没有生成latch。细思之,这个逻辑的实现方法是对的。

如果实现一句话的唯一方法是锁存器,那么才会综合出锁存器吧。最后附一张管脚图:

顶顶顶顶顶顶顶顶顶顶顶顶顶

抢得一手好沙发