fpga作为从机与stm32进行spi通信

时间:10-02

整理:3721RD

点击:

正在做stm32和fpga的spi通信,通信测试基本完成但是出现了一下的一点问题。我用stm32的spi口给fpga发送一个字节的数据,然后将fpga采集到的数据作为输出,然后用Quartus II的signaltap看数据结果,如图

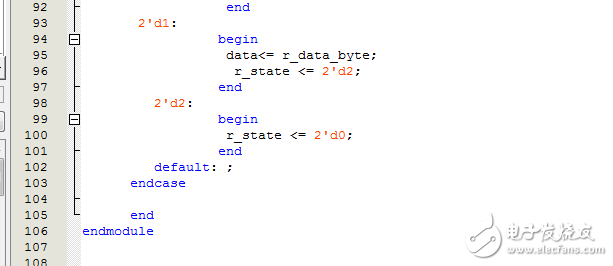

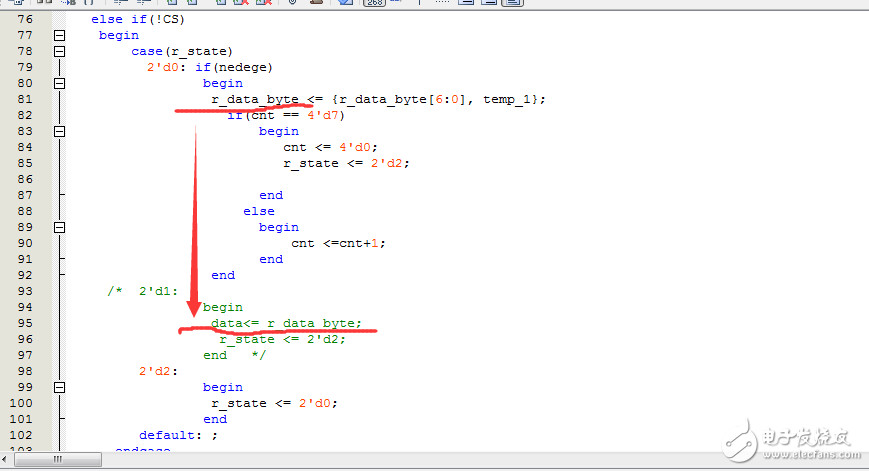

我最先将fpga采集到的数据r_data_byte在下一个状态赋给另一个寄存器data,但是当我进行测试时,刚开始第一个数据正常,但是当我修改stm32发送的数据后,signaltap看到的结果就不对了,同时置位标志位flag也异常。然后我就改为直接用r_data_byte作为输出,如图

我最先将fpga采集到的数据r_data_byte在下一个状态赋给另一个寄存器data,但是当我进行测试时,刚开始第一个数据正常,但是当我修改stm32发送的数据后,signaltap看到的结果就不对了,同时置位标志位flag也异常。然后我就改为直接用r_data_byte作为输出,如图

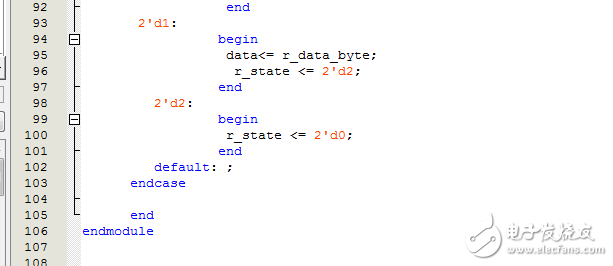

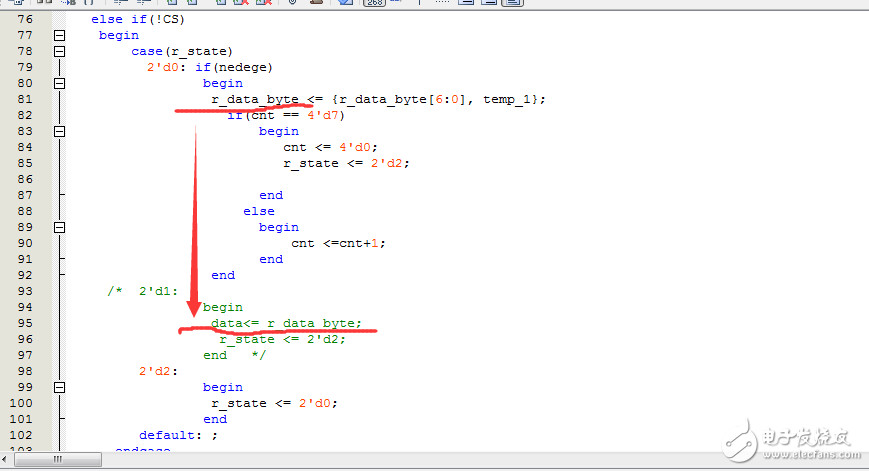

这样发现,无论怎么改变stm32发送的数据,接收数据都是正确的,我就是不明白为什么前面一种情况,在下一个状态赋给另一个寄存器会出现错误,第一种情况的前后仿真时序都是正确的,请大家帮忙看看前面一种情况的问题出在哪里

这样发现,无论怎么改变stm32发送的数据,接收数据都是正确的,我就是不明白为什么前面一种情况,在下一个状态赋给另一个寄存器会出现错误,第一种情况的前后仿真时序都是正确的,请大家帮忙看看前面一种情况的问题出在哪里

我最先将fpga采集到的数据r_data_byte在下一个状态赋给另一个寄存器data,但是当我进行测试时,刚开始第一个数据正常,但是当我修改stm32发送的数据后,signaltap看到的结果就不对了,同时置位标志位flag也异常。然后我就改为直接用r_data_byte作为输出,如图

我最先将fpga采集到的数据r_data_byte在下一个状态赋给另一个寄存器data,但是当我进行测试时,刚开始第一个数据正常,但是当我修改stm32发送的数据后,signaltap看到的结果就不对了,同时置位标志位flag也异常。然后我就改为直接用r_data_byte作为输出,如图

这样发现,无论怎么改变stm32发送的数据,接收数据都是正确的,我就是不明白为什么前面一种情况,在下一个状态赋给另一个寄存器会出现错误,第一种情况的前后仿真时序都是正确的,请大家帮忙看看前面一种情况的问题出在哪里

这样发现,无论怎么改变stm32发送的数据,接收数据都是正确的,我就是不明白为什么前面一种情况,在下一个状态赋给另一个寄存器会出现错误,第一种情况的前后仿真时序都是正确的,请大家帮忙看看前面一种情况的问题出在哪里2‘d1状态没法运行 看把2‘d0中的s_state修改下 看行不行

cnt应该用CS再做一次复位,r_data_byte赋值给data,可以用flag作为标志位,发送端CS为什么没有拉高?不太懂你一个数据包里有多少bit

一次接收16bit的数据

程序贴出来看

小编,最近我也在搞这个,可否指导一下

小编,最近我也在搞这个,可否指导一下

小编,最近我也在搞这个,可否指导一下。

小编,最近我也在搞这个,可否指导一下。

小编,最近我也在搞这个,可否指导一下。

小编,最近我也在搞这个,可否指导一下。

你有什么问题?

求大佬 分享32 和 FPGA spi 通信代码?谢谢大佬