+ 快速匹配算法实现-结项

时间:10-02

整理:3721RD

点击:

感谢“电子发烧友论坛”和“xilinx”举办的这次Artix-7试用活动,使我有机会接触到了xilinx系列fpga,经过一段时间的摸索学习,使我受益匪浅。

先说下这个算法的背景,之前一个项目,需要检测位置信息,使用时,将传感器靠近钢轴,轴上面有特定的条纹,通过传感器检测轴表面磁场的特性,来判断当前在哪个位置。功能类似于磁栅,但需要是绝对位移的检测,检测长度长达数米,理想精度为0.1mm,同时需要保证传感器可以和轴有一定的间隙,以免磨损传感器。

传感器可检测的磁场范围约100mm,这就要求全长数米的轴上,不能出现任何两个100mm长区域的磁场相同,或过于接近。这个经过多种编码方式评估,最终确定了一种既方便加工,又保证无相似区域的编码方式。

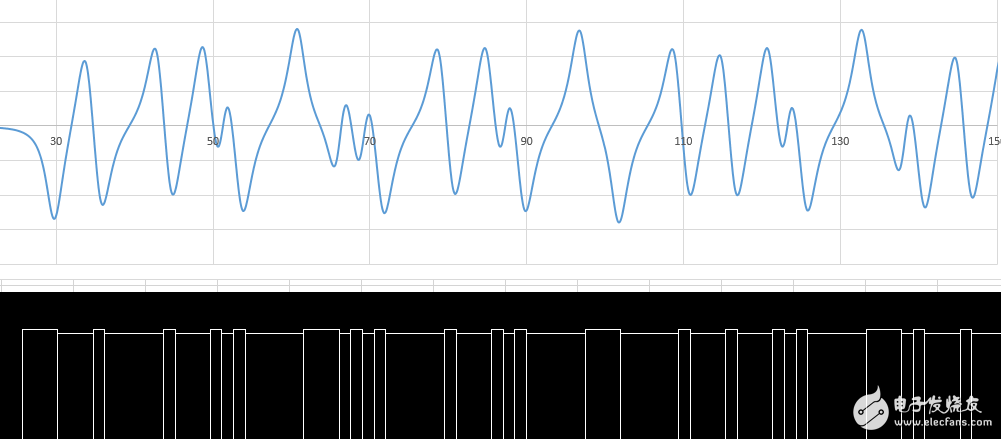

下图是其中的一段编码和仿真的磁场。

检测时,就需要对测的一段波形,和这整个长度的数据进行匹配,找到最佳匹配点,即是当前位置。

数据全长100K,点间距为0.1mm;传感器可检测到64个点,点间距为1.4mm;故匹配时,还需做14的倍增,才可。

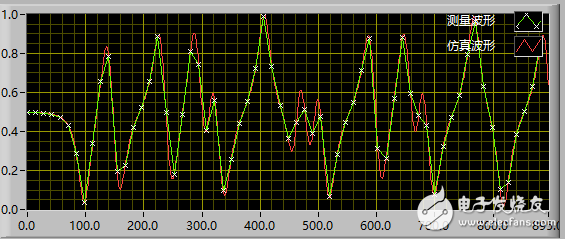

这里最佳匹配点算法,采用的是最常用的方法。将64个点,和仿真数据之间的误差累加;遍历全部100k次,选择误差最小点即为最匹配点。

匹配算法

最佳匹配位置

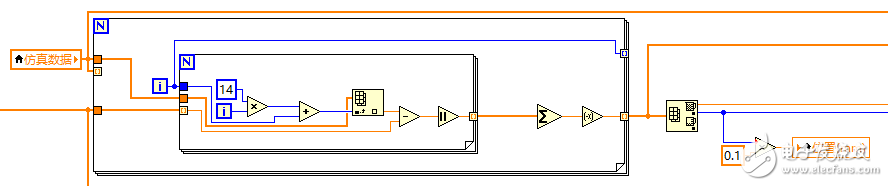

经在LabVIEW上验证,算法可行且可靠。

但此项目关键在于实时性,客户要求达到几十Hz的更新速率,在pc端测试,每次更新需要300ms左右,已超出运行时间,换用高端arm处理器,最快也需要2秒时间。故只能考虑使用fpga实现此算法。

考虑100K的数据,每个数据读取64次,共需读取6.4M次,对于100M主频的ram,仅访内存的时间就达到了64ms,必须另找新的处理方式。

考虑到计算100K次误差,第n次误差计算要读取64次数据,第n+1次误差计算也需要读取64次数据,这两次读取的数据有63个是一样的,故可以考虑使用流水线形式处理。每次读取一个数据,同时计算64次,64个寄存器分别累加此误差,同时第一个寄存器已计算完成,最后一个寄存器则还只有一个误差累家。这样,只要读取100k+64次即可实现所有点的匹配算法。

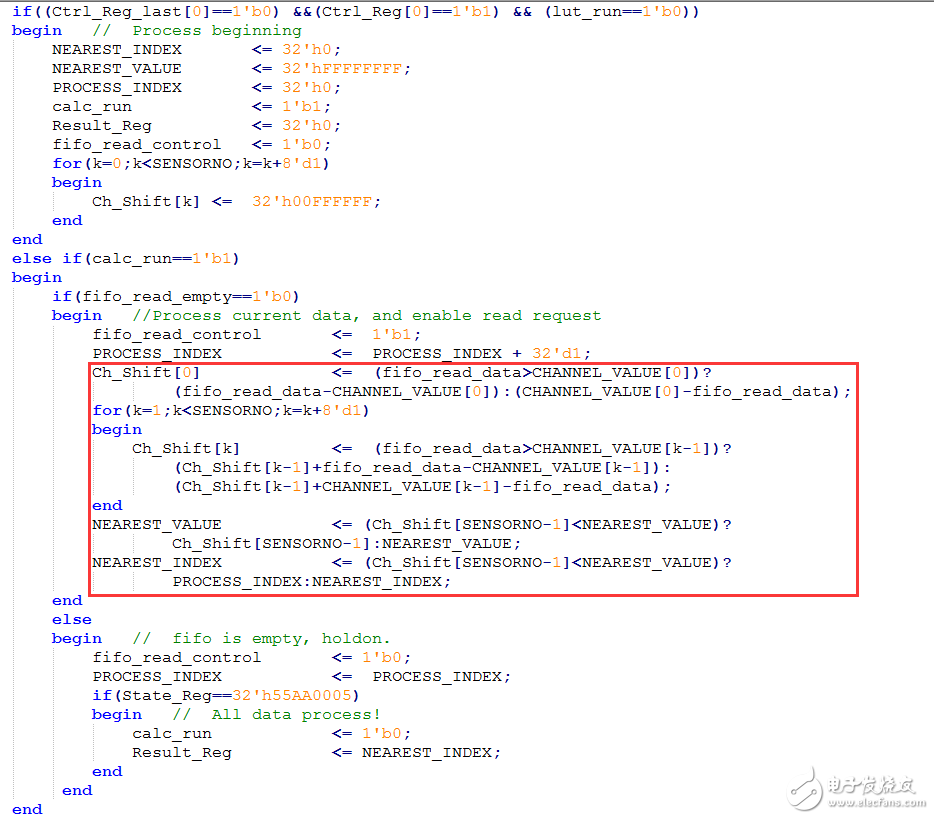

下图为核心算法,红色框内为流水线部分。

当然此举也将导致耗用大量fpga资源,算法虽然简单,但毕竟有64级并行计算,中间还有个判断符号的过程,而且为保证系统可扩展性,算法里都是按32位数据类型处理的。

经过实际测试,此流水线方式处理,100K次数据只需8.6ms即可处理完成。

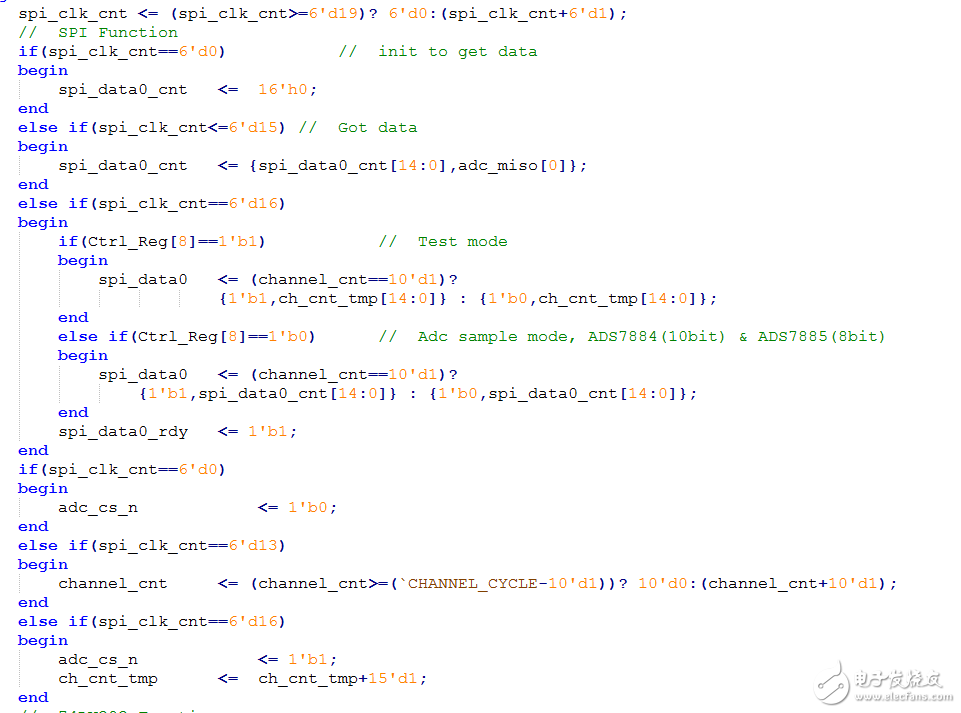

同时需要实现传感器接口,传感器为spi接口类型,以下为核心代码。

此spi接口可将spi数据读取到fifo中,并存储到指定位置。

每次看到结项两个字感觉都值得好好学习学习

只能佩服,小编真的好棒~~~

好东西啊好东西啊。