关于锁相环中输出选取的问题

时间:10-02

整理:3721RD

点击:

大家好,我先整体跟大家说一下我的思路:就是一个IP核中的锁相环有四个时钟输出(例如CLK0、CLK1、CLK2、 CLK3),我现在想通过四个按键,从四个中选择一个作为输出(例如按键A B C D一一对应四个时钟输出)。

我现在把IP核的XCO格式文件添加到我的工程中,我又做了一个按键的程序,接下来请问我该怎么例化或者说怎么将两者联系到一起?新手初接触FPGA希望大家多多帮忙。

我现在把IP核的XCO格式文件添加到我的工程中,我又做了一个按键的程序,接下来请问我该怎么例化或者说怎么将两者联系到一起?新手初接触FPGA希望大家多多帮忙。

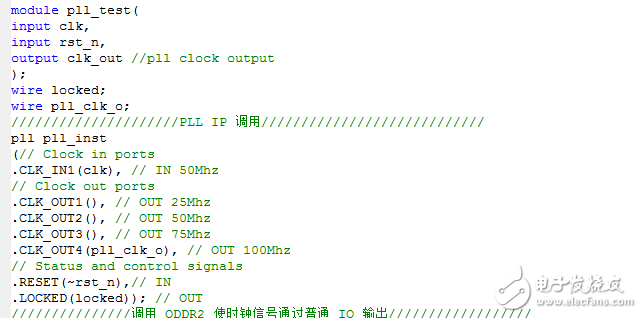

这是我做的ip核,里面有四个输出

通过判断按键的状态,用数据选择的方式,选择你想要输出的时钟信号!

这个还是很基础,有两种实现思路:

思路一:

1.例化4个你想要频率的锁相环:分别为

pll_clk_o1,pll_clk_o2,pll_clk_o3,pll_clk_o4

2.做一个4路选择器;

3.选择器输入是你的按键输入,输出为你想要的时钟;

always @(*) begin

case(key)

1: clk<=pll_clk_o1;

2: clk<=pll_clk_o2;

3: clk<=pll_clk_o3;

4: clk<=pll_clk_o4;

default:1: clk<=pll_clk_o1;

endcase

end

或者

assign clk=(key==1)?pll_clk_o1:

(key==2)?pll_clk_o2:

(key==3)?pll_clk_o3:

(key==4)?pll_clk_o4:pll_clk_o1;

思路二:

就是将pll ipcore中分频倍频系数用parameter赋值,在外部用defparam控制,具体参数要进行计算

学习一下相关资料

你好,能留一下你的联系方式么,我想在线请教下

看不懂啊。

请教不敢当

我QQ:578232974