Artix-7 50T FPGA板卡文件安装与使用

时间:10-02

整理:3721RD

点击:

感谢电子发烧友论坛给予这次试用机会,一直想试用一下Xilinx FPGA,苦于没有太多机会。这次就让我好好领略一下Xilinx最新7系列FPGA的高大上。

首先介绍一下安装板卡文件的优势:

1、板载资源无需添加管脚约束

2、部分Vivado自带IP可以直接配置到相关资源

板卡文件其实就是一个xml文件,对板卡的资源进行了相关描述与约束设计。方便我们在使用过程对板卡资源进行合理配置。举例说明,在调用GPIO IP核点亮LED时,一般情况下,需要设置引脚并约束到板卡上固定的LED引脚。但有了板卡文件后,Vivado会自动识别,LED这个资源与哪一个IP核匹配,同时约束好相应的管脚。

下面介绍安装板卡文件的步骤:

1、下载好板卡文件7A50T_Board_Definition_Files_Vivado_2014_2

https://products.avnet.com/opasdata/d120001/medias/common/4/$v2/7A50T_Board_Definition_Files_Vivado_2014_2.zip

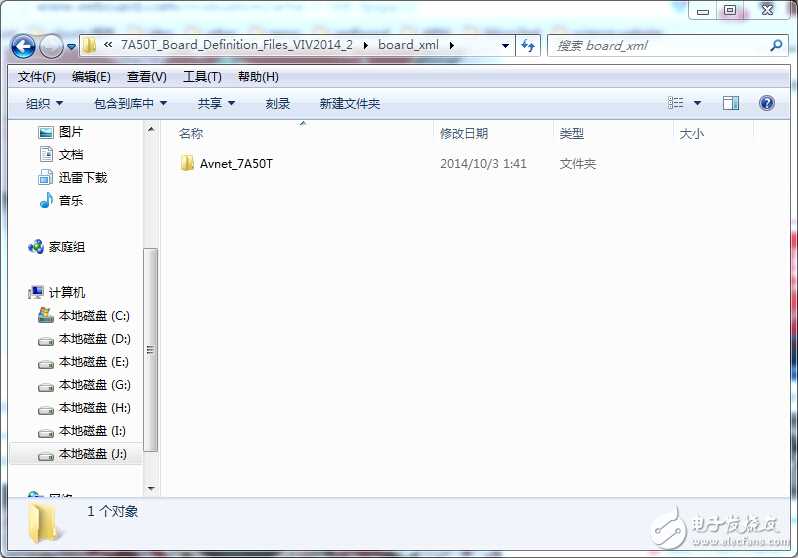

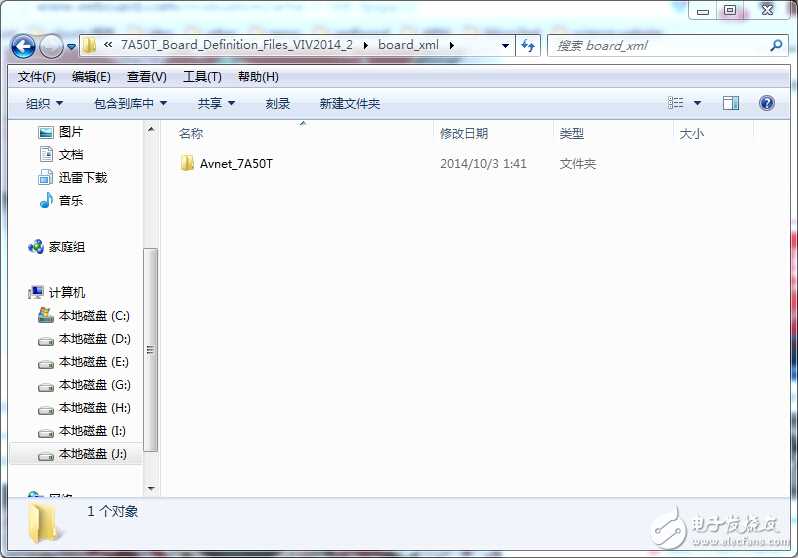

2、解压得到板卡文件,在7A50T_Board_Definition_Files_VIV2014_2\board_xml路径下,Avnet_7A50T文件夹就是板卡文件。

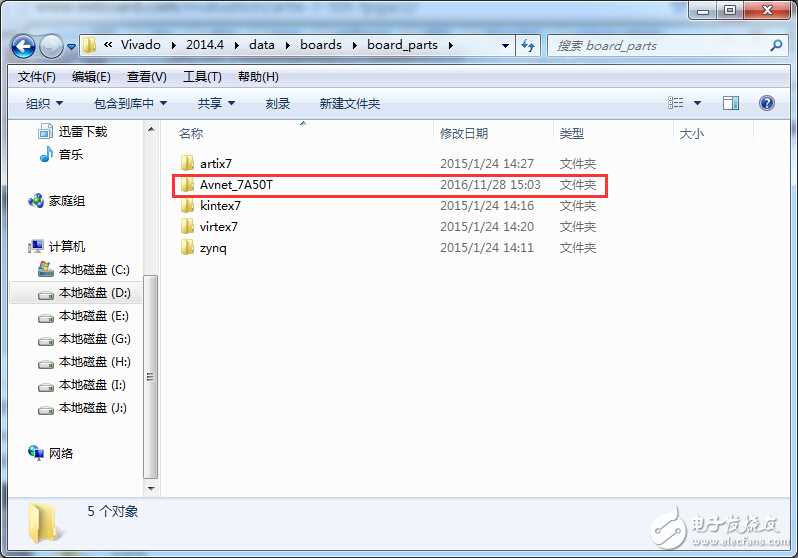

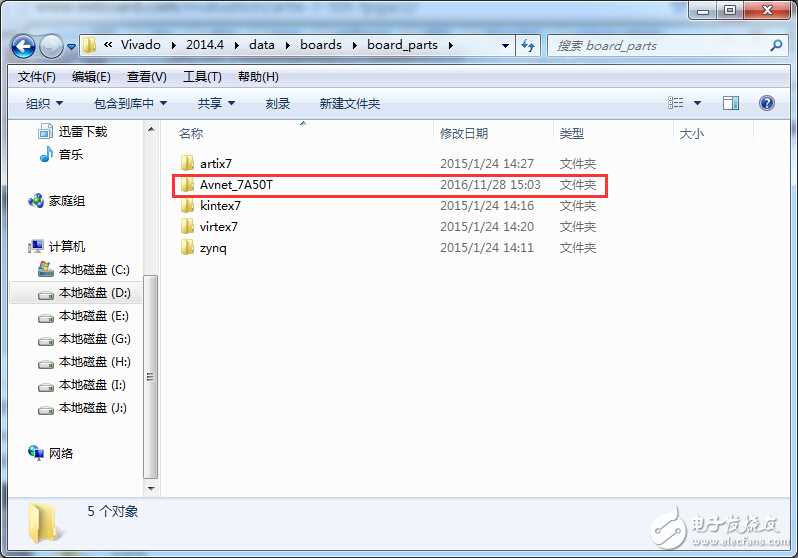

3、拷贝Avnet_7A50T文件夹,复制到C:\Xilinx\Vivado\2014.4\data\boards\board_parts Vivado软件安装的板卡文件下。(本人将Vivado 2014.4安装在C:\Xilinx\路径下,根据自己的安装位置切换目录)

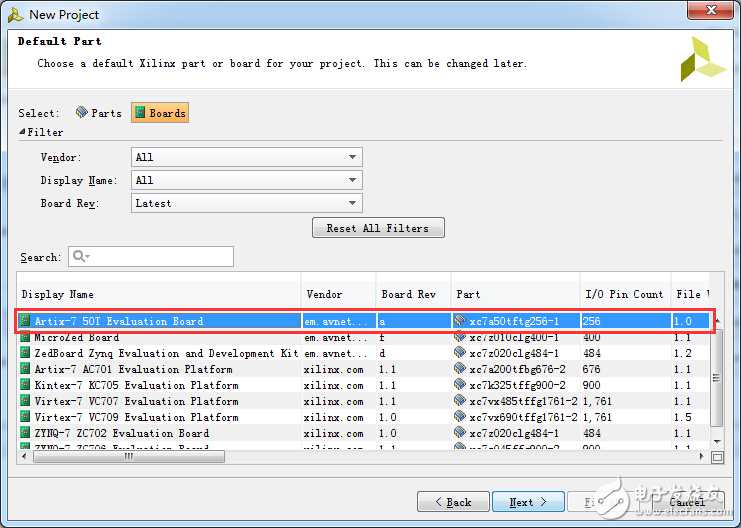

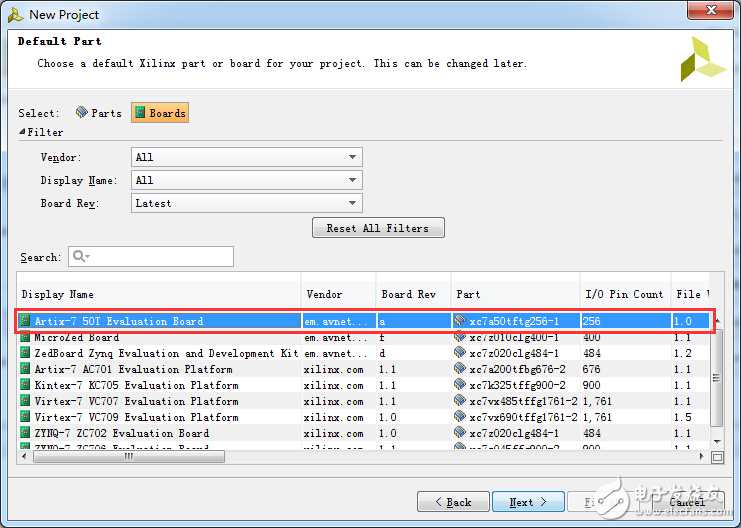

4、重启Vivado,创建工程时,在器件板卡选型时,可以选择Boards面板,选择Artix-7 50T Evaluation Board板卡。无需知道FPGA芯片详细信息。

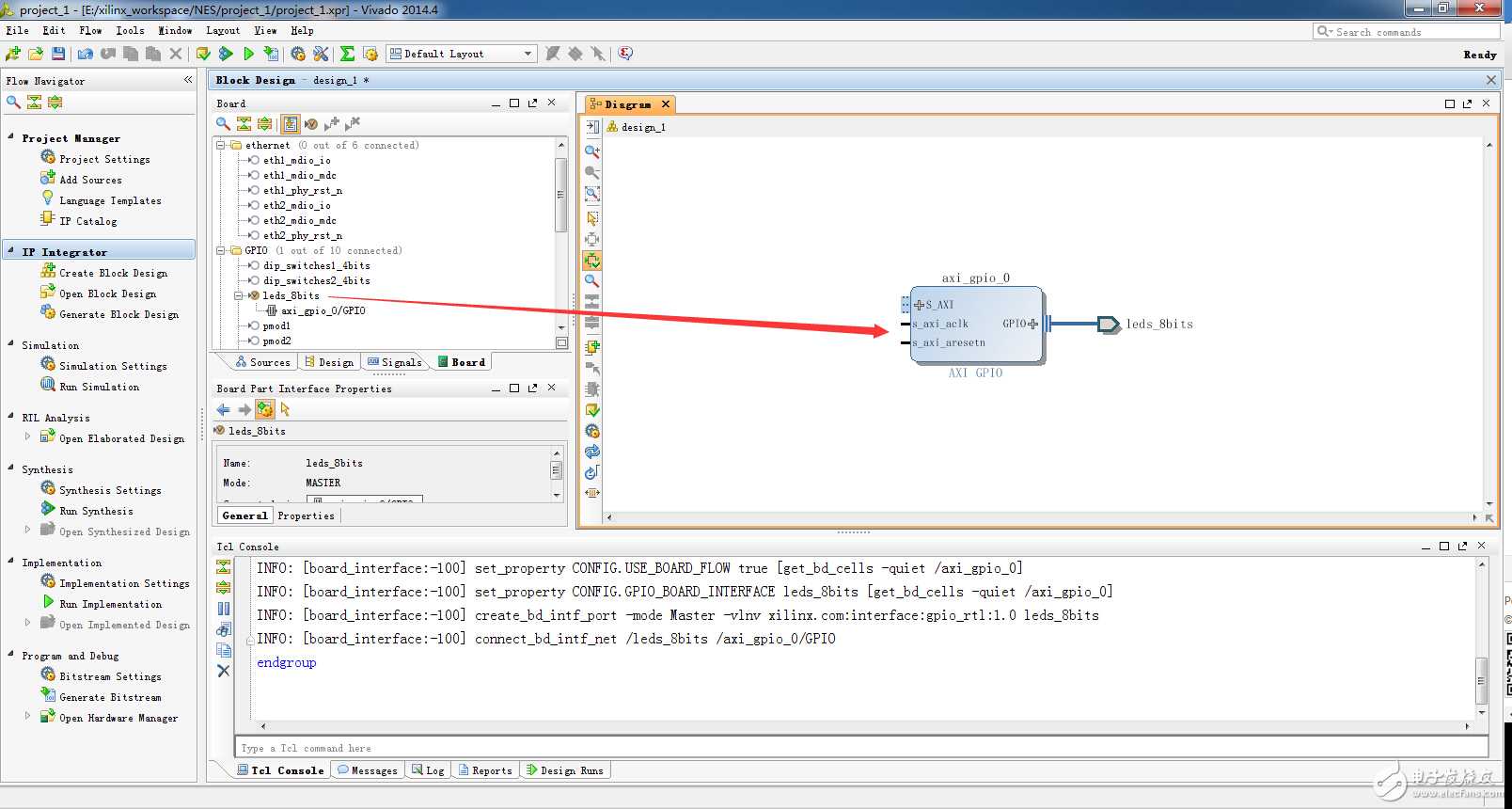

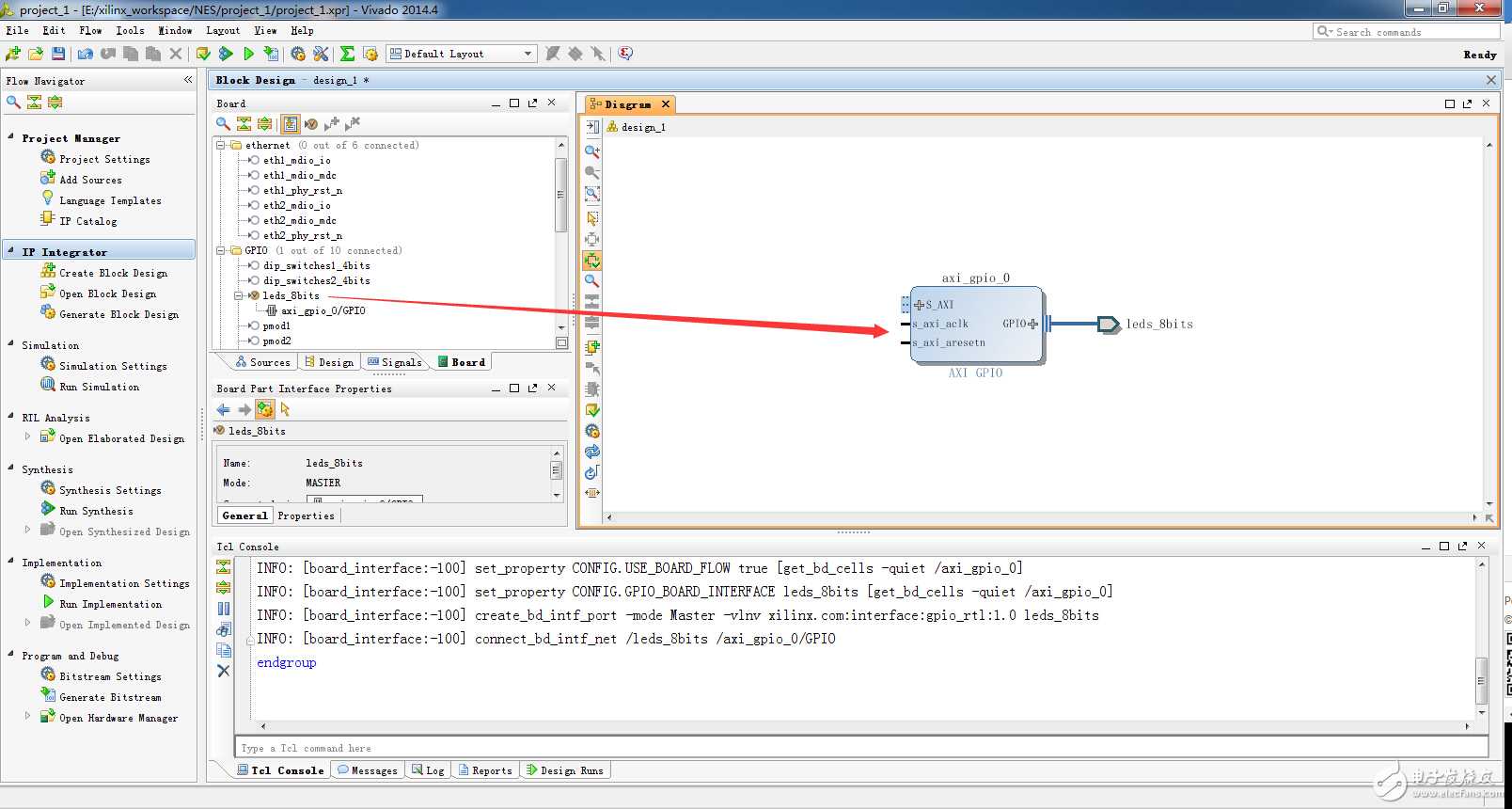

5、在Block Design设计时,可以直接拖动板卡资源到设计面板中。

这就是简单的LED实例化过程,在嵌入式设计时,相当方便用户使用。

首先介绍一下安装板卡文件的优势:

1、板载资源无需添加管脚约束

2、部分Vivado自带IP可以直接配置到相关资源

板卡文件其实就是一个xml文件,对板卡的资源进行了相关描述与约束设计。方便我们在使用过程对板卡资源进行合理配置。举例说明,在调用GPIO IP核点亮LED时,一般情况下,需要设置引脚并约束到板卡上固定的LED引脚。但有了板卡文件后,Vivado会自动识别,LED这个资源与哪一个IP核匹配,同时约束好相应的管脚。

下面介绍安装板卡文件的步骤:

1、下载好板卡文件7A50T_Board_Definition_Files_Vivado_2014_2

https://products.avnet.com/opasdata/d120001/medias/common/4/$v2/7A50T_Board_Definition_Files_Vivado_2014_2.zip

2、解压得到板卡文件,在7A50T_Board_Definition_Files_VIV2014_2\board_xml路径下,Avnet_7A50T文件夹就是板卡文件。

3、拷贝Avnet_7A50T文件夹,复制到C:\Xilinx\Vivado\2014.4\data\boards\board_parts Vivado软件安装的板卡文件下。(本人将Vivado 2014.4安装在C:\Xilinx\路径下,根据自己的安装位置切换目录)

4、重启Vivado,创建工程时,在器件板卡选型时,可以选择Boards面板,选择Artix-7 50T Evaluation Board板卡。无需知道FPGA芯片详细信息。

5、在Block Design设计时,可以直接拖动板卡资源到设计面板中。

这就是简单的LED实例化过程,在嵌入式设计时,相当方便用户使用。