基于FPGA的可变祖冲之(ZUC)算法的设计与实现

码力分享基于FPGA的可变祖冲之(ZUC)算法的设计与实现

1:概述

基于FPGA的可变祖冲之(ZUC)算法的设计与实现

软件:ISE 语言:Verilog HDL,C语言

2:功能

通过加入可配置模块(如S盒等),设计并实现参数可重配置的可变祖冲之算法。

3:实现方法

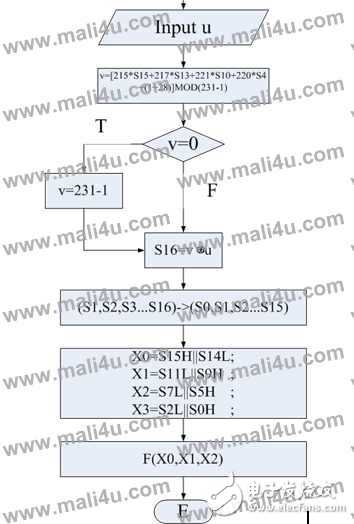

S盒设计流程如图1所示:

图1S盒流程图

整个工程的输入是32bits的U,输出是一个32位字的密钥流。

1)第一个模块是线性移位寄存器,其主要输入输出端口如图2所示;实现的主要功能是根据。

LFSRWithInitialisationMode(U)

{

1.v=215S15+217S13+221S10+220S4+(1+28)S0 mod (231-1);

2. If v=0, then set v=231-1;

3. s16=v⊕u;

4. If s16=0, then set s16=231-1;

5. (s1,s2, …,s15,s16)→(s0,s1, …,s14,s15).

得到(s0,s1, …,s14,s15). LFSR的初始状态初始密钥是可以改变的。

2)第二个模块是位重组,其主要端口如图2所示;实现的主要功能是根据

Bitreorganization()

{

1. X0=s15H || s14L;

2. X1=s11L || s9H;

3. X2=s7L || s5H;

4. X3=s2L ||s0H.

}

形成4个32位字的X0,X1,X2,X3。

3)第三个模块是非线性函数,其主要端口如图2所示;实现的主要功能是函数F输出一个32位字W。这个模块的具体实现主要是利用ROM。

R1=S(L1(W1L||W2H));

R2=S(L2(W2L||W1H)).

上述的L1,L2是利用的线性变换:

L1(X)=X⊕(X > 1。

(2)工作模式

LFSR的工作模式,在没有收到任何输入,它的工作原理为将S16代替v与U的异或。

2)位重组设计方案:

将从线性反馈移位寄存器得到的S(i),计算得出位重组数据X0=s15H || s14L; X1=s11L || s9H; X2=s7L || s5H; X3=s2L ||s0H.

3)非线性函数设计方案:

首先是通过32bit到32bit的线性变换,然后将得到的数据作为地址输入到ROM中,也即S盒中,输出得到非线性函数的值。再通过相关计算得到了函数F输出一个32位字W。4)4)可变模块的设计方案和整体衔接的设计方案:

将线性变换得到的数据作为地址输入到ROM中,也即S盒中,输出得到非线性函数的值。再通过相关计算得到了函数F输出一个32位字W。这就实现了可变模块与整体设计方案的衔接。

详细点感觉更好 啊

我现在也在写ZUC,能交流一下吗?QQ244816711

我现在也在写ZUC,能交流一下吗?QQ244816711

这个算法是什么呢?