不同时钟域之间的多周期路径

时间:10-02

整理:3721RD

点击:

高速到低速

file:///C:/Users/ADMINI~1/AppData/Local/Temp/enhtmlclip/Image.png

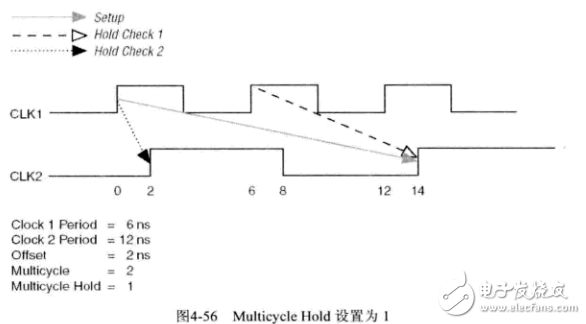

上图给定的条件:

如果不使用多周期约束,quartus II的时序分析工具将按照数据建立时间setup time=2ns(即offset时间)要求进行检查,如果设置了多周期路径为2,那么建立时间要求就放松了,就可以延伸到目的端的第二个时钟上升沿处(即14ns)(Note:建立时间即:数据必须要在14ns之前从源端到达目的端,即数据延时小于14ns)

上图将Multicycle Hold =1,这样quartus II时序分析时,将检查如下两个保持时间关系:

所以为了满足该电路正常工作,数据延时必须大于8ns,小于14ns

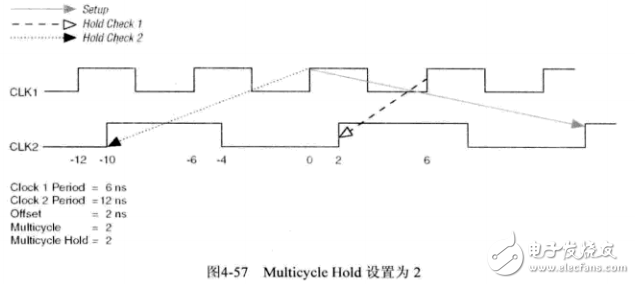

看下面一副图的设定。

file:///C:/Users/ADMINI~1/AppData/Local/Temp/enhtmlclip/Image(1).png

setup time 仍然是14ns。

将多周期保持(Multicycle Hold)设置为2,那么计算保持时间(Hold time),检查的参考时钟要向前移动一个目的端的时钟周期。quartus II 分析时序时,检查如下两个保持时间:

所以为了满足该电路正常工作,数据延时必须大于-4n(为负表示肯定能满足,延时不肯能为负数),小于14ns(只需满足data delay 小于14ns即可)。

可以看出在Multicycle Hold=2时,约束条件更加宽松了。

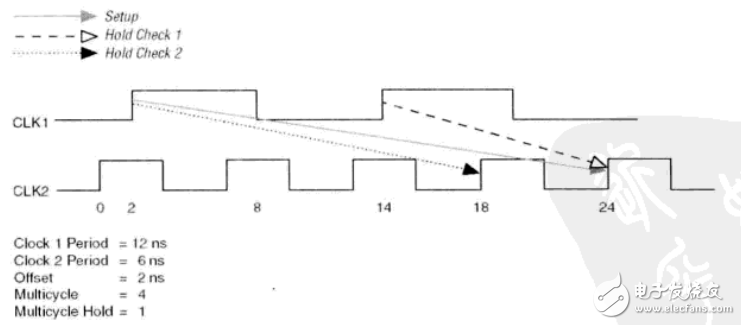

低速到高速多周期路径

两个时钟之间也有2ns的offset。

这里设置Multicycle =4,那么其建立时间向后延伸4个周期,Setup time=(24ns-2ns)=22ns

Multicycle Hold=1,同样这里检查两个保持时间关系

这样数据延时必须大于16ns,小于22ns

file:///C:/Users/ADMINI~1/AppData/Local/Temp/enhtmlclip/Image.png

上图给定的条件:

- 高速时钟到低速时钟

- 两个时钟有2ns的offset

- 源端时钟是目的端时钟频率两倍

如果不使用多周期约束,quartus II的时序分析工具将按照数据建立时间setup time=2ns(即offset时间)要求进行检查,如果设置了多周期路径为2,那么建立时间要求就放松了,就可以延伸到目的端的第二个时钟上升沿处(即14ns)(Note:建立时间即:数据必须要在14ns之前从源端到达目的端,即数据延时小于14ns)

上图将Multicycle Hold =1,这样quartus II时序分析时,将检查如下两个保持时间关系:

- Hold Check1:(空心箭头,检查源端下个Launch edge 发出的数据,不会被目的端当前的Latch edge 锁存),最小的数据延时为8ns(14ns-6ns)(Note:即数据经过Tco+Tdata延时需要大于8ns,电路才能正常工作 )

- Hold Check2:(实心箭头,检查源端此刻Launch edge 发出的数据,不会被目的端上一次Latch edge 锁存),最小数据延时为2ns(2ns-0ns)(Note:即数据经过Tco+Tdata延时需要大于2ns,电路才能正常工作 )

所以为了满足该电路正常工作,数据延时必须大于8ns,小于14ns

看下面一副图的设定。

file:///C:/Users/ADMINI~1/AppData/Local/Temp/enhtmlclip/Image(1).png

setup time 仍然是14ns。

将多周期保持(Multicycle Hold)设置为2,那么计算保持时间(Hold time),检查的参考时钟要向前移动一个目的端的时钟周期。quartus II 分析时序时,检查如下两个保持时间:

- Hold Check1:空心箭头,检查源端下个Launch edge 发出的数据,不会被目的端当前的Latch edge 锁存。最小的数据延时为-4ns(2ns-6ns)。

- Hold Check2:实心箭头,检查源端此刻Launch edge 发出的数据,不会被目的端前一个Latch edge 锁存。最小的数据延时为-10ns(-10ns-0ns)。

所以为了满足该电路正常工作,数据延时必须大于-4n(为负表示肯定能满足,延时不肯能为负数),小于14ns(只需满足data delay 小于14ns即可)。

可以看出在Multicycle Hold=2时,约束条件更加宽松了。

低速到高速多周期路径

两个时钟之间也有2ns的offset。

这里设置Multicycle =4,那么其建立时间向后延伸4个周期,Setup time=(24ns-2ns)=22ns

Multicycle Hold=1,同样这里检查两个保持时间关系

- Hold Check1:空心箭头,检查源端下个Launch edge 发出的数据,不会被目的端当前的Latch edge 锁存。最小的数据延时为10ns(24ns-14ns)。

- Hold Check2:实心箭头,检查源端此刻Launch edge 发出的数据,不会被目的端前一个Latch edge 锁存。最小的数据延时为16ns(18ns-2ns)。

这样数据延时必须大于16ns,小于22ns