各位大神,基于FPGA控制ADC0804的程序,有疑问

时间:10-02

整理:3721RD

点击:

module ADC0804(clk_50M,rst,INTR,DB,CS,WR,RD);

input clk_50M,rst,INTR;//clk_50M是外部FPGA时钟信号 rst是复位信号 INTR是ADC转换结束信号

input [7:0] DB; //DB是ADC转换结果数据

output CS,WR,RD; //CS是片选信号 WR是启动转换控制信号 RD是外部读取转换结果控制信号,从ADC端口送出

reg CS,WR,RD;

reg [7:0] data; //data用来存取FPGA读进来的DB数据

reg [15:0] cnt; //cnt用来计数给50MHZ分频

reg [2:0] state;

//------------------------------------------------------------------

parameter state0 = 3'b000, //用状态机控制ADC的时序转换

state1 = 3'b001,

state2 = 3'b010,

state3 = 3'b011,

state4 = 3'b100,

state5 = 3'b101;

//------------------------------------------------------------------------

always @(posedge clk_50M)

begin

if(!rst) //rst有效的话,状态机和计数复位

begin

state<=state0;

cnt <= 0;

end

else

begin

cnt <= cnt +1'b1;

if(16'd50 == cnt) //1us采样一次

begin

cnt <= 0;

case(state)

state0: //状态0 控制ADC初始化

begin

RD = 1;

CS = 1;

WR = 1;

state <= state1;

end

state1: //状态1,控制ADC开始转换

begin

CS = 0;

WR = 0;

RD = 1;

state <= state2;

end

state2: //状态2,等待INTR信号变低,[size=14.3999996185303px]采样结束

begin

CS = 1;

WR = 1;

RD = 1;

if (0 == INTR)

state <= state3;

end

state3: //状态3

begin

CS = 0;

WR = 1;

RD = 0;

state <= state4;

end

state4: //状态4,从ADC读入模拟电压转换之后的数据

begin

data <= DB;

state <= state0;

end

endcase

end

end

end

endmodule

///////////////////////////////////////////////////////////////////////////////////////////////////

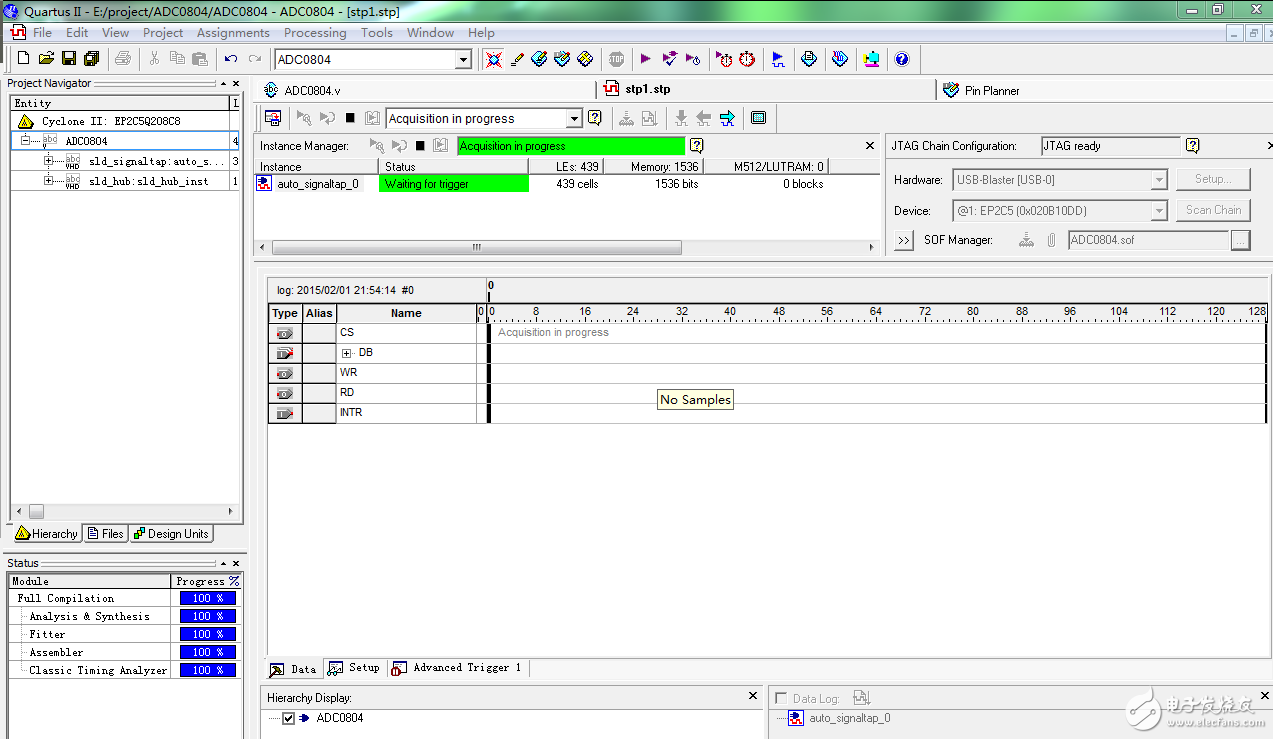

用quartusII的signaltap II logic analyaer(逻辑分析仪)检测输出信号如图:

[size=14.3999996185303px]状态机的时序问题我也反复看过,貌似没有问题。各位大神,对于没有结果输出时什么原因呢?

你确定会用Sigtap?确定把采样时钟加到Sigtap里面去了么(例如你程序里面的50M时钟)?如果这点能确定,那就看下你的时钟是否有,或者时钟管脚分配没有。

贴图中的 fclk是多少M的频率?程序中1us采一次,是不是采不到INTR信号,还有一点state3时,不需要讲cs拉低吧,这样写状态机的编码风格不好,若要简单,可采用二段式的方式