软核的设计中添加DM9000A后引脚的分配问题

时间:10-02

整理:3721RD

点击:

小弟刚刚在做一个关于DM9000A模块的设计!遇到一点问题!请教各位高手!

软核的设计中添加DM9000A后引脚的分配问题! 谢谢高手指点!

源码:

软核的设计中添加DM9000A后引脚的分配问题! 谢谢高手指点!

源码:

- module DM9000A(//HOST Side: Avalon slave signals

- iDATA,

- oDATA,

- iCMD,

- iRD_N,

- iWR_N,

- iCS_N,

- iRST_N,

- iCLK,

- iOSC_50,

- oINT,

- //DM9000A Side: export signals

- ENET_DATA,

- ENET_CMD,

- ENET_RD_N,

- ENET_WR_N,

- ENET_CS_N,

- ENET_RST_N,

- ENET_INT,

- ENET_CLK );

- //HOST Side

- input[15:0] iDATA ;

- input iCMD ;

- input iRD_N ;

- input iWR_N ;

- input iCS_N ;

- input iRST_N ;

- input iCLK ;

- input iOSC_50 ;

- output [15:0] oDATA ;

- output oINT ;

- //DM9000A Side

- output [15:0] ENET_DATA ;

- output ENET_CMD ;

- output ENET_RD_N ;

- output ENET_WR_N ;

- output ENET_CS_N ;

- output ENET_RST_N ;

- output ENET_CLK ;

- input ENET_INT ;

- reg [15:0] TMP_DATA ;

- reg ENET_CMD ;

- reg ENET_RD_N ;

- reg ENET_WR_N ;

- reg ENET_CS_N ;

- reg ENET_CLK ;

- reg [15:0] oDATA ;

- reg oINT ;

- //写使能状态下将ENET_DATA位置高阻状态

- assign ENET_DATA=ENET_WR_N?16'hzzzz:TMP_DATA ;

-

- always@(posedge iCLK or negedge iRST_N)

- begin

- if(!iRST_N)

- begin

- TMP_DATA <=0 ;

- ENET_CMD <=0 ;

- ENET_RD_N <=1 ;

- ENET_WR_N <=1 ;

- ENET_CS_N <=1 ;

- oDATA <=0 ;

- oINT <=0 ;

- end

- else

- begin

- oDATA <=ENET_DATA ;

- oINT <=ENET_INT ;

- TMP_DATA <=iDATA ;

- ENET_CMD <=iCMD ;

- ENET_CS_N <=iCS_N ;

- ENET_RD_N <=iRD_N ;

- ENET_WR_N <=iWR_N ;

- end

- end

- always@(posedge iOSC_50)

- ENET_CLK <= ~ENET_CLK ;

- assign ENET_RST_N = iRST_N ;

- endmodule

DM9000A引脚分配问题

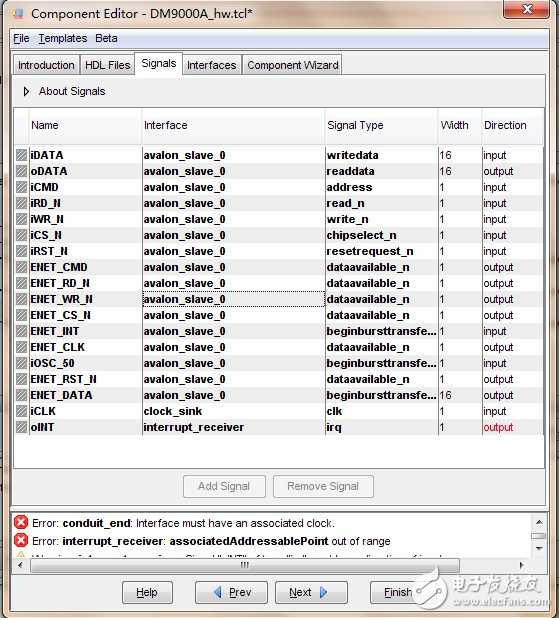

未有加入信号相关的驱动信号,从错误的提示中可以看出,conduit_end这个信号没有相关时钟,中断号需要重新分配一下...

端口除了输入输出需要配置以外,它还有相应的依赖信号,比如,这个输出信号它用了其他的某个信号,这种关系像是依赖一样,比如,没有时钟输入,分频模块就没有意义,在应用别人的IP核的时候,还需要认真读读他人些的IP核使用手册,自己写的话,也需要纳入考虑中。