写一段HDL代码实现对输入时钟三分频的功能

时间:10-02

整理:3721RD

点击:

请写一段HDL 代码实现对输入时钟三分频的功能(要求输出时钟占空比为50%)

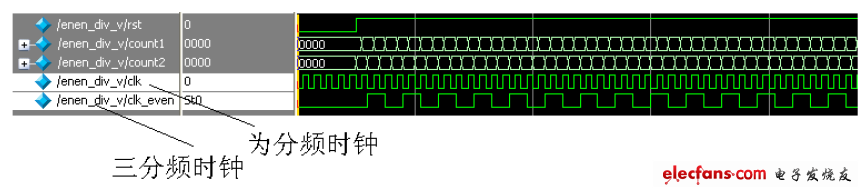

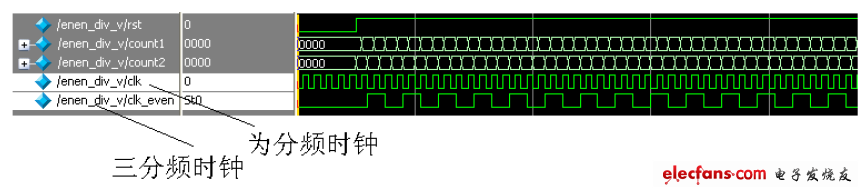

modelsim 仿真结果:

- module even_division(clk,rst,count1,count2,clk_even);

- input clk;

- input rst;

- output [3:0] count1;

- output [3:0] count2;

- output clk_even; //????±è 50%μ?·??μ

- reg [3:0] count1,count2;

- reg clkA,clkB;

- reg clktet;

- wire clk_even,clk_re;

- parameter N = 3;

- assign clk_re = ~clk;

- assign clk_even = clkA | clkB;

- always @(posedge clk) begin

- if(!rst) begin

- count1 > 1;

- always @(posedge clk) begin

- if(!rst) begin

- clkA > 1;

- always @(posedge clk_re) begin

- if(!rst) begin

- clkB <= 0;

- end

- else if(count2 < (N-1)) begin

- if(count2 == NB) begin

- clkB <= ~clkB;

- end

- end

- else begin

- clkB <= ~clkB;

- end

- end

- reg [3:0] cnt10;

- always @(posedge clk) begin

- if(!rst) begin

- cnt10 <= 0;

- end

- else if(cnt10==4) begin

- cnt10 <= 0;

- end

- else begin

- cnt10 <= cnt10 + 1'b1;

- end

- end

- always @(posedge clk) begin

- if(!rst) begin

- clktet <= 0;

- end

- else if(cnt10 == 4) begin

- clktet <= ~clktet;

- end

- end

- endmodule

modelsim 仿真结果:

不错,我之前只弄了个5分频,学习了!