CDMA反向链路波形发生器的设计

Maxim设计了一个容易实现的CDMA基带调制发生器用于对其蜂窝手机发射通道中的各种产品进行电路评估。此设计包含一个高密度的可编程逻辑器件、一个晶体振荡器和一对匹配的低通滤波器提供所需的正交输出波形。由复杂可编程逻辑器件(CPLD)实现的数字电路是基于IS95标准的。使用4.9152MHz晶振驱动CY37256 CPLD产生1.2288MHz的数字信号输出,可以为输出低通滤波器提供精确的I/Q (同相和正交)比特流。测量MAX2361发射机IC的ACPR,将结果与使用Agilent E4433B任意波形发生器作为参考信号源时观察到的ACPR进行比较就可以证实波形发生系统的性能。使用上述两种方案的ACPR试验室测量结果的一致程度保持在0.5dB以内。

概述

Maxim设计了一个容易实现的CDMA基带调制发生器用于对其蜂窝手机发射通道中的各种产品进行电路评估。此设计包含一个高密度的可编程逻辑器件、一个晶体振荡器和一对匹配的低通滤波器提供所需的正交输出波形。由复杂可编程逻辑器件(CPLD)实现的数字电路是基于IS95标准的。使用4.9152MHz晶振驱动CY37256 CPLD产生1.2288MHz的数字信号输出,可以给输出低通滤波器提供精确的I/Q (同相和正交)比特流。测量MAX2361发射机IC的ACPR,将结果与使用Agilent E4433B任意波形发生器作为参考信号源时观察到的ACPR进行比较就可以证实波形发生系统的性能。使用上述两种方案的ACPR试验室测量结果的一致程度保持在0.5dB以内。

本文提供了CDMA反向链路波形发生器的数字部分,描述了设计中的一些问题及解决方法。

数字系统描述

标准的CDMA信号发生器

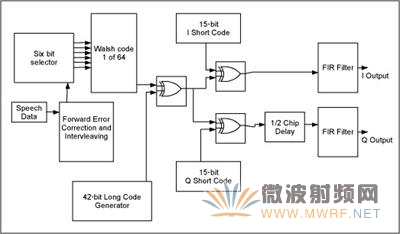

图1所示为CDMA反向信道发生器的框图。

CDMA发生器由以下几个部分组成:

数字数据源。在蜂窝电话中为话音编码数据。

编码和交织(interleaving)功能部分。

Walsh码发生器。

最大长度的42位长PN (伪噪声)发生器,所谓"长码"的标准即参照此处。

3个模2的混频器或者异或门。

两个"短码",15位PN最大长度移位寄存器。

一个1/2码片延时,等于(813.8ns / 2)即406.9ns。

一对匹配的有限冲击响应(FIR)低通滤波器。

图1. 标准的CDMA反向链路发生器

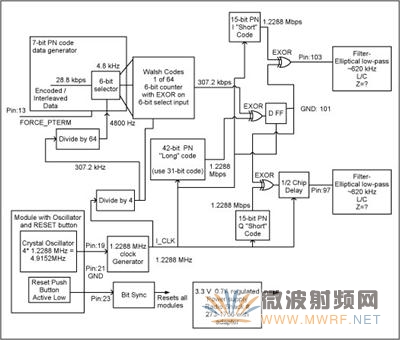

对设计进行简化

为了进行实际测量,对编码进行一些简化。由于对频谱的影响很小,删除与前向纠错(FEC)和交织部分有关的模块。为了模拟CELP编解码数据源,使用7位最大PN发生器。

使用42位最大长度移位寄存器长码实现31位的长PN码。这样作是为了保留CPLD中的寄存器并使设计的验证更加迅速。42位PN发生器,以1.2288MHz的速度移位一周需要约三百六十万秒。 (简单的计算一下就可发现测试装置必须连续41天无干扰地工作!)。提高验证42位PN发生器速度的一个方法是加快时钟的速度。即使时钟为20MHz,完成一周的验证仍然要花费2.5天。使用31位的PN码,在20MHz时钟下运行时间将小于两分钟,这个时间对测试来说比较合理。

用简单的基于电感、电容的无源滤波器取代输出端的数字(FIR)低通滤波器。本文不讨论这些滤波器的复杂性和重要性,但是可以告诉那些对此感兴趣的读者,设计中使用的是带有相位均衡的600kHz 7阶椭圆低通滤波器。其性能关键点是,740kHz衰减为-45dBc,881kHz及更高频率的衰减为-65dBc。发射频谱的带宽、滚降速率以及受此影响的观察到的ACPR与这些滤波器的品质有直接的联系。

图2所示为本项目中使用的简化的框图。

图2. 最后实现的CDMA反向链路发生器

设计中的细节问题

本文不试图把设计和实现中的每一个细节都呈现出来。用几个关键的部分来说明设计技术和解决方案。我们并不想把读者都变成Verilog专家。

Walsh码发生器

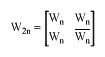

Walsh码发生器在文献中通常用矩阵符号表示:

等式1.

等式1.

建立Walsh向量时假设初始矩阵为W1 = 0。等式中Walsh矩阵右下角区域带有一个横杠的Wn表示矩阵中的每一位都逻辑取反。Walsh矩阵中的每一行都能用一些异或门和一个6位的计数器产生。在观察到这一点之前,使用Verilog代码并在CPLD中产生Walsh矩阵似乎是一件令人生畏的事情。将Verilog代码列在这里只是作为一个示例。

| module walsh( clk, resetn, select, wout); | ||

| //Walsh code generator. Selects one out of N = 64. |

| input clk, resetn; | ||

| input [5:0]select; // vector to select which walsh code is generated | ||

| output wout; | ||

| reg [5:0] cntval; | ||

| // intermediate terms to keep output exor size small. | ||

| reg [5:0] p ; | ||

| reg t01, t23, t45; // these registers are used to pipeline the EXOR section | ||

| reg s0, s1; // more pipeline registers for EXOR | ||

| always ? (negedge resetn or posedge clk) | ||

| begin | ||

| if(!resetn) // Is it time to reset?? | ||

| begin | ||

- 一种改善W-CDMA手机用功率放大器线性度的新方法(10-06)

- 利用射频功率检测器和高效切换器增强CDMA PA功率(05-02)

- 对比ADI两代TD-SCDMA射频IC得到的启示(05-02)

- 超小尺寸、低功耗CDMA收发器解决方案(06-27)

- 基于LDMOS的TD-SCDMA射频功率放大器(04-24)