CDMA反向链路波形发生器的设计

| cntval <= 0; // initialize the counter register | ||

| end | ||

| else | ||

| begin | ||

| cntval <= cntval + 1; //Warp does an efficient job implementing this. | ||

| end | ||

| end | ||

| always ? (negedge resetn or posedge clk) | ||

| begin | ||

| if(!resetn) // Is it time to reset?? | ||

| begin | ||

| p[5:0] <= 0; // initialize all registers associated with this section. | ||

| t01 <= 0; | ||

| t23 <= 0; | ||

| t45 <= 0; | ||

| s0 <= 0; | ||

| s1 <= 0; | ||

| end | ||

| else | ||

| begin | ||

| p <= cntval & select ; | ||

| t01 <= p[0] ^ p[1] ; // the ^ symbol is the exclusive OR operation. | ||

| t23 <= p[2] ^ p[3] ; | ||

| t45 <= p[4] ^ p[5] ; | ||

| s0 <= t01 ^ t23; | ||

| s1 <= t45; | ||

| end | ||

| end | ||

| assign wout = s0 ^ s1 ; // a last bit of async. Logic to generate the final output | ||

| endmodule | ||

在上面的Verilog代码中,注意构成运算所采取的安全措施并尽可能使用同步逻辑。使用同步技术对设计有两方面的好处:

- 亚稳定性条件被降到最低。

- 逻辑功能与CPLD结构能够有效对应。

为了使用现代的硬件描述语言实现数字设计,必须熟悉目标硬件。大多数CPLD具有逻辑门 -> 寄存器的规则结构,Verilog代码如果遵循同样的结构将有利于高效地对应到CPLD中。这样,工程师就能支配整个综合处理的过程。如果忽略了这一点,在Verilog代码中使用了多级异步逻辑,CPLD装配器将使逻辑迅速膨胀并很快超过目标CPLD的容量,在实现异或功能时尤其如此。这里用Verilog代码描述的Walsh码发生器通过中间寄存器使用流水线技术实现异或功能,执行过程非常紧凑。

Walsh码发生器Verilog代码还体现了可靠性设计的多个要点。在每一个"always ?"部分的开始都进行一次复位条件的测试,所有相关的寄存器根据需要调整或清零。这种总是以一个已知的状态开始工作的方法是一种已被证实的用来实现可靠工作的技术。代码中还使用了单独的部分实现6位计数器,另一部分用来创造异或逻辑以选择正确的Walsh向量作为输出。最后,注意如何使用注释,在Verilog中以//符号标识。

PN发生器

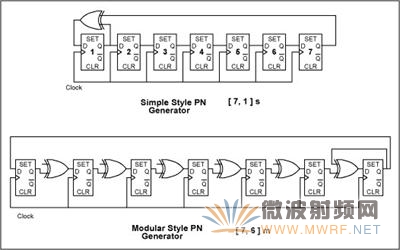

CDMA发生器使用4个PN发生器。有两种基本的方法可以实现最大长度码移位寄存器:简单的反馈结构和模块化结构(见图3)。

图3. 简单的和模块化的PN发生器实例

当与所用的逻辑相比码率(码片)较慢并且反馈抽头的数量很小时,简单的PN发生器是可以接受的。当抽头数目增加时,简单的方法开始呈现出局限性,通过多级异步逻辑的延时不断增加,限制了可用的最大时钟速率。简单的PN发生器在本设计中用于模拟随机数据,时钟速率为4.8kHz。

模块化的PN发生器使用更多的逻辑门,EXOR操作是在线性寄存器的每一级并行执行的。由此对CPLD造成的负担并不十分严重,因为写入的Verilog代码只在需要的时候使用EXOR结构,其它时候使用简单的D类触发器。

本设计中使用的CDMA特定多项式为:

短码I:I(X):= X15 + X13 + X9 +X8 + X7 + X5 + 1

短码Q:Q(X):= X15 + X12 + X11 + X10 + X6 + X5 + X4 + X3+ 1

长码:LC(X):= X42 + X35 + X33 + X31 + X27 + X26 + X25 + X22 + X21 + X19 + X18 + X17 + X16 + X10 + X7 + X6 + X5 + X3 + X2 + X1 + 1

实现短I码的Verilog代码为:

| module i_code_s( clock, resetn, i_code_out); | ||

| // Generate the 15-bit PN code using the polynomial | ||

| // x15 + x13 + x9 + x8 + x7 + x5 + 1 |

| input clock, resetn; | ||

| output i_code_out; | ||

| reg [15:1]pi; | ||

| always ?(posedge clock or negedge resetn) | ||

| if(!resetn) | ||

| begin | ||

| pi <= 15';b111111111111111; // init the shift register with ones | ||

| end | ||

| else | ||

| begin // here starts the modular shift register | ||

| pi[1] <= pi[15]; | ||

| pi[5:2] <= pi[4:1] ; | ||

| pi[6] <= pi[5] ^ pi[15]; | ||

| pi[7] <= pi[6]; | ||

| pi[8] <= pi[7] ^ pi[15]; | ||

| pi[9] <= pi[8] ^ pi[15]; | ||

| pi[10] <= pi[9] ^ pi[15]; | ||

| pi[13:11] <= pi[12:10]; | ||

- 一种改善W-CDMA手机用功率放大器线性度的新方法(10-06)

- 利用射频功率检测器和高效切换器增强CDMA PA功率(05-02)

- 对比ADI两代TD-SCDMA射频IC得到的启示(05-02)

- 超小尺寸、低功耗CDMA收发器解决方案(06-27)

- 基于LDMOS的TD-SCDMA射频功率放大器(04-24)