CMOS图像传感器IBIS5-B-1300的驱动时序设计

数字处理器、I/O以及系统管理资源完美地结合在一起,使之具有更高层次、更广泛的应用。

2.2 控制时序的设计

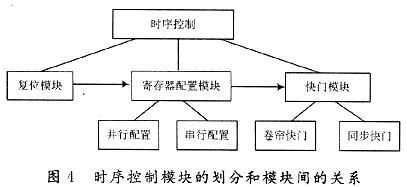

该设计采用VHDL硬件描述语言,根据自顶向下的设计方法,将时序控制部分分为三个模块:复位模块、寄存器配置模块和快门模块。由于寄存器有两种配置方式,快门模式也有两种,因而后两部分都可以再细分为两个小模块。三个大的模块有严格的先后关系,必须在前一模块已完成后,才可开始后一模块。图4显示模块的划分及其关系。

复位模块是用来产生图像传感器所需的SYS_RE_SET信号,使传感器正常复位,内部寄存器清零,为寄存器的配置做好准备。

寄存器配置模块是用来配置图像传感器内部的12个寄存器,提供传感器工作所需的参数和方式。其中,参数有积分时间、积分方式(单斜率或多斜率)、X序列发生器的时钟间隔、SS序列发生器的时钟间隔、亚采样方式、开窗位置及大小等。

快门模块用于产生传感器工作所需的一些控制信号,针对快门方式的不同给出所需的时序控制信号。在同步快门的设计中,该设计采用单斜率积分,在此设计基础上多斜率积分容易实现。

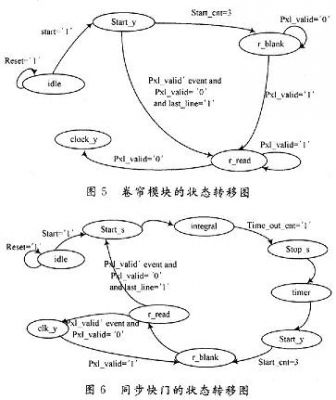

该设计采用VHDL对各模块时序进行编程。其中,快门模块使用状态机来实现各状态之间的转换(图5显示了卷帘模块的状态转移图,图6显示了同步快门的状态转移图)。全局时钟和ADC时钟采用DCM即数字时钟管理单元来实现。

3 实验结果

3.1 仿真结果

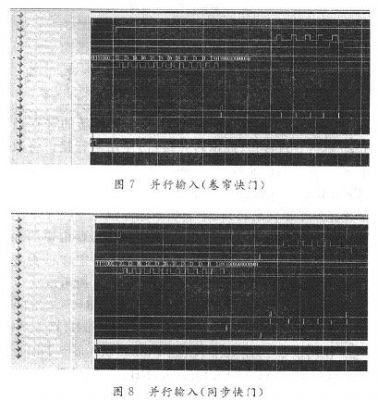

时序控制电路设计完毕后,需要对各部分进行功能仿真、逻辑综合以及综合后仿真,最后对整个系统进行综合、布局布线,完成时序仿真。对各模块编程并仿真通过后,将各模块加载到主函数top中,采用并行的寄存器配置方式,对卷帘和同步两种快门方式进行仿真,在Modelsim中的仿真结果如图7,图8所示。

3.2 成像结果

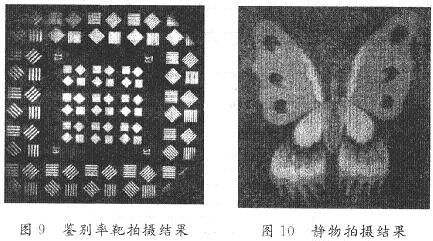

将此驱动时序应用于相机系统,在全帧输出模式(1 280×1 024)下,对鉴别率靶和静物进行拍摄,实验结果如图9,图10所示。由所拍摄结果可以看出,图像清晰稳定,无明显变形,CMOS图像传感器满足了成像的需求。

4 结语

图像传感器驱动时序的正确与否对其能否正常工作起着决定性的作用。本文在分析CMOS图像传感器IBIS5-B-1300工作时序的基础上,设计了两种寄存器配置方案和两种快门方式,并用FPGA内嵌的数字时钟管理单元(DCM)完成了系统时钟和ACD时钟的设计。实验结果表明,所设计的驱动时序可以满足该图像传感器的驱动要求。

发布者:小宇

CMOS 图像传感器 IBIS5-B-1300 相关文章:

- 图像传感器市场突破60亿美元,CMOS将占主导地位(05-22)

- 德国机器视觉产业增长显著,CCD/CMOS传感器产品前景看好(06-23)

- 美国Ziptronix对5层CMOS和光电二极管进行3维封装(03-18)

- CMOS成像技术让照相功能大显身手(07-01)

- 高速CMOS图像传感器及发展趋势(07-08)

- 市场趋于饱和,CMOS图象传感器已经日薄西山?(07-31)