美国Ziptronix对5层CMOS和光电二极管进行3维封装

时间:03-18

来源:技术在线

点击:

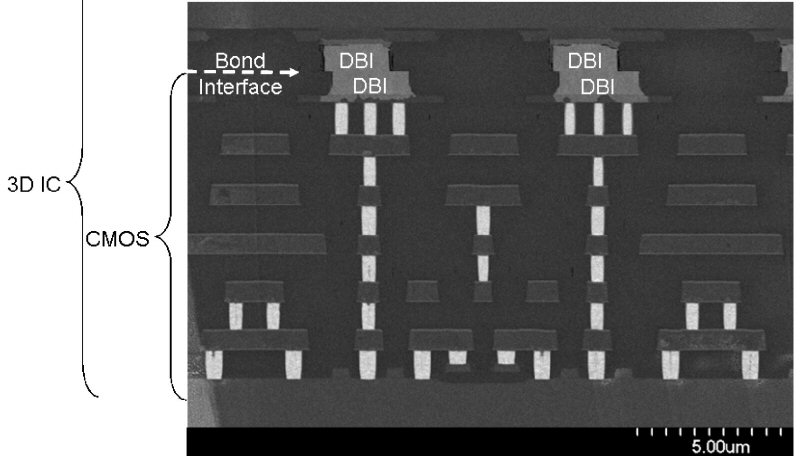

美国Ziptronix与Raytheon Vision Systems(RVS)合作,对5层CMOS元件和光电二极管进行了3维层叠。在层叠时,采用了Ziptronix开发的名为"Direct bond interconnect(DBI)"的3维封装技术。

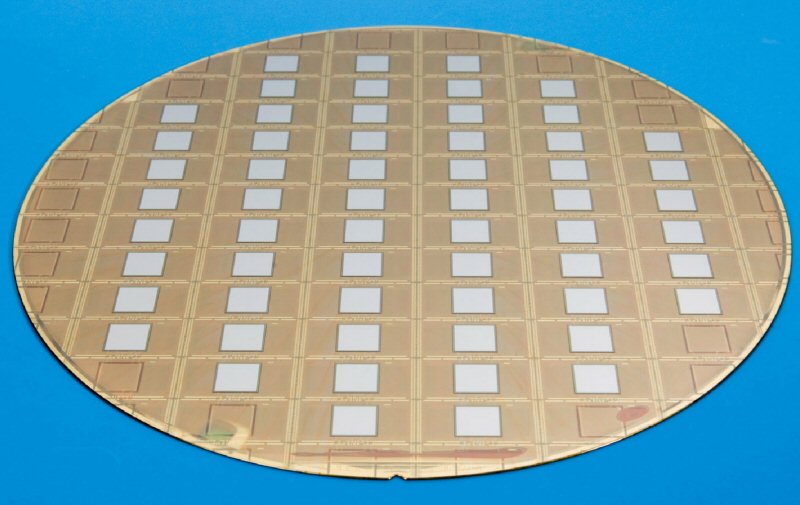

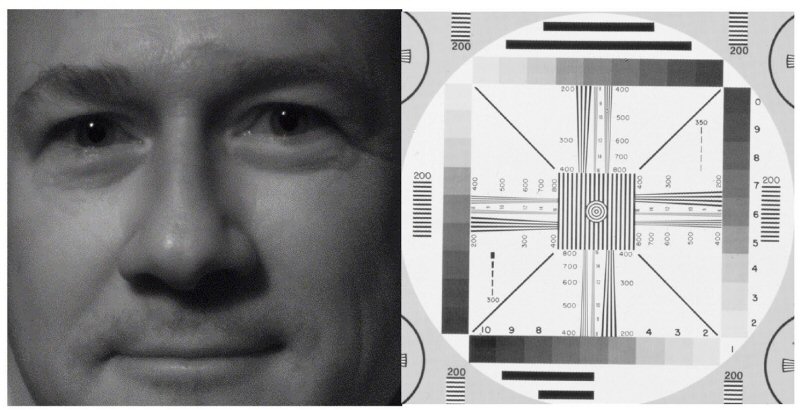

采用DBI技术,在芯片与晶圆、晶圆与晶圆接合时,也可在室温下实现3维封装。布线间距在10μm以下,布线宽度为2μm左右。此次在形成有CMOS元件的晶圆上,层叠了RVS公司的芯片。布线间距为8μm。可在确保接合部连接性的同时,通过所有光电二极管获取图像。(记者:河合 基伸)

|

| 对5层CMOS元件和光电二极管进行3维封装 |

|

| 在形成有CMOS元件的晶圆上层叠RVS的芯片 |

|

| 通过3维封装的芯片获取的图像 |

CMOS 相关文章:

- 图像传感器市场突破60亿美元,CMOS将占主导地位(05-22)

- 德国机器视觉产业增长显著,CCD/CMOS传感器产品前景看好(06-23)

- CMOS成像技术让照相功能大显身手(07-01)

- 高速CMOS图像传感器及发展趋势(07-08)

- 市场趋于饱和,CMOS图象传感器已经日薄西山?(07-31)

- 赛普拉斯CMOS图像传感器将胶片和数字视频结合用于电影拍摄(11-27)