高速CMOS图像传感器及发展趋势

时间:07-08

来源:赛普拉斯半导体 定制图像传感器事业部标准产品经理 Pieter Willems

点击:

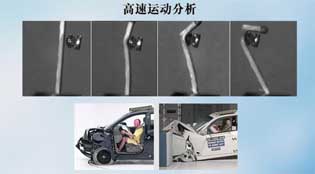

文本将介绍高速CMOS|0">CMOS图像传感器的类型及其应用市场。高速传感器适用于通用、高端或定制的高速摄像头,而这些摄像头可用于科研、汽车碰撞检测、高速扫描、机器视觉和军事研究等要求较高的帧速率运动捕获的领域。传感器分辨率从VGA级直到1万像素不等,有的能以每秒10,000次全帧速率工作。

传感器架构可由两分式、四分式或一个像素阵列组成。输出可为并行模拟输出, 或一个10位数字输出或数字串行LVDS|0">LVDS输出。每个输出可高达每秒5,000万次的采样速度,这样就能实现每秒55亿像素的吞吐量。迄今为止,该图像传感器是具有最高连续像素吞吐量的一款。图像质量至少达到10位精度,因此摄像头数字化之后,数据吞吐量可为每秒55Gbit。这样高速的应用通常需要6个电晶体快照像素,且需要较高的灵敏度和动态范围。图像传感器的灵敏度很大程度上取决于像素尺寸,而大的像素尺寸就需要大面积特定应用的定制图像传感器。内部多路复用技术可支持更高帧速率的随机窗口。如果将窗口大小缩至较小的ROI(圈选目标区域),那么最快速度器件的帧速率可达每秒170,000帧。大多数传感器都采用0.25工艺。

目前,CMOS是高速成像所青睐的技术。在当前市场中,我们可以发现高速图像传感器有三大发展趋势,一是向极高速方向发展,二是向片上特性集成方向发展,三是向通用高速图像传感器方向发展。

分辨率和帧速率相结合,发挥着重要的作用。目前,我们可以推出1024×1024像素的图像传感器,工作速度达到每秒5,000个全帧。如果模数转换为10 位的话,那么这就是说摄像头上的总数据速率可达每秒55Gbit。为了实现传感器上极高的数据速率和高图像质量,尤其是对这种高敏感度的应用而言,我们不仅要设计出正确的电子线路,还要确保整个线路布局实现良好的平衡性。这就是说,电源线路应实现极佳的分布,而且布局中每个线路节点的所有光学和杂散光灵敏反应都应得到很好的控制。并需要采用低功耗模块设计,以确保满足整体功耗要求。

高速成像领域还有另一种趋势,就是把高速 ADC|0">ADC、时序发生器、LVDS发射器和校正算法的片上集成趋势。这种图像传感器通常在速度和灵敏度方面不如上述图像传感器,但在易用性和系统集成功能方面颇有长处。目前市场上新兴的第三种图像传感器就是通用高速图像传感器。具有模拟输出或不具有时序发生器功能的老式(简单式)通用图像传感器正在被速度更快、更复杂的图像传感器所取代。这种新型图像传感器使我们能在较短时间内就设计出通用高速摄像头。

6晶体管像素

赛普拉斯推出的大多数高速图像传感器使用了所谓的6晶体管(6T)像素。这种图像传感器有一点非常重要,就是其管线化全局快门特性。就全局快门而言,所有像素都同时启动和终止光集成,这对高速应用控制所有像素的运动影像模糊非常重要。全局快门技术使图像传感器能固定高速运动场景。下图给出了典型的高速捕获顺序(小弹头击中火柴棍)。管线特性确保像素阵列在读取期间就能进行下一帧像素中的光集成工作,这样才能确保帧速率不受集成时间的影响。

典型的高速捕获顺序 为了实现尽可能高的敏感度,采集光电荷并将其转换为电压的光电二极管应设计得尽可能小型化,以尽可能减少光电二极管的寄生电容。此外,像素填充因数(像素开放区域与光敏区域之比)应尽可能大。我们可采用N-well像素专利技术,再配合光电二极管周边的P-well开口,就能实现光电二极管小型化和较大的填充因数。除了高敏感度之外,我们还应使像素存储电容,与光实现良好的屏蔽并且减少泄漏, 确保它不会造成任何噪声。该像素架构在像素读数期间的信号存储方面实现了良好的性能。但这种像素架构尚缺乏像素的固定图案噪声校正功能,该功能必须在图像传感器以外的系统上完成。更快的速度 图像传感器的速度是指精度和帧速率的乘积,反映出传感器的像素速率。在非常高端的高速成像市场中,人们对速度的需求是没有止境的。在高端市场中,客户希望通过高级摄像头实现极高的全帧速率,比如汽车碰撞检测。 只有采用并行模拟输出才能实现这样极高的速度,但并行模拟输出(最多128个输出)也会对摄像头系统的集成提出挑战。这种类型的图像传感器架构比较简单:包括一个可被分为若干像限的6T像素阵列,几个并行高速模拟总线以及用于驱动输出的并行输出放大器。

|

- 赛普拉斯推出通用CMOS图像传感器(10-11)

- 凌力尔特公司推出3个低功率16位、25Msps至125Msps模数转换器(ADC)系列(10-24)

- 安森美增添4款高分辨率器件到获奖的PYTHON CMOS图像传感器系列(09-16)

- 赛普拉斯为用于机器视觉与运动分析应用的 LUPA 高速 SXGA CMOS(10-17)

- 东芝为可拍照手机提供小型化的320像素和200像素SENSOR(10-08)

- 图像传感器市场突破60亿美元,CMOS将占主导地位(05-22)